# THE CRAY-1 COMPUTER SYSTEM

# THE CRAY - 1 COMPUTER SYSTEM

The Cray Research, Inc. CRAY-1 Computer System is a large-scale, general-purpose digital computer featuring vector as well as scalar processing, a 12.5 nanosecond clock period, and a 50 nanosecond memory cycle time. The CRAY-1 is capable of executing over 80 million floating point operations per second. Even higher rates are possible with programs that take advantage of the vector features of the computer.

The CRAY-1 is an effective host processor for local computer networks and time-sharing networks. Cray Research provides hardware and software interfaces that link the CRAY-1 with other manufacturer's computer systems. This approach allows users to add the CRAY-1 to existing computing facilities.

The CRAY-1 is particularly adapted to the needs of the scientific community and is especially useful in solving problems requiring the analysis and prediction of the behavior of physical phenomena through computer simulation. The fields of weather forecasting, aircraft design, nuclear research. geophysical research, and seismic analysis involve this process. For example, the movements of global air masses for weather forecasting, air flows over wing and airframe surfaces for aircraft design, and the movements of particles for nuclear research, all lend themselves to such simulations. In each scientific field, the equations are known but the solutions require extensive computations involving large quantities of data. The quality of a solution depends heavily on the number of data points that can be considered and the number of computations that can be performed. The CRAY-1 provides substantial increases with respect to both the number of data points and computations so that researchers can apply the CRAY-1 to problems not feasibly solvable in the past.

## CONFIGURATION

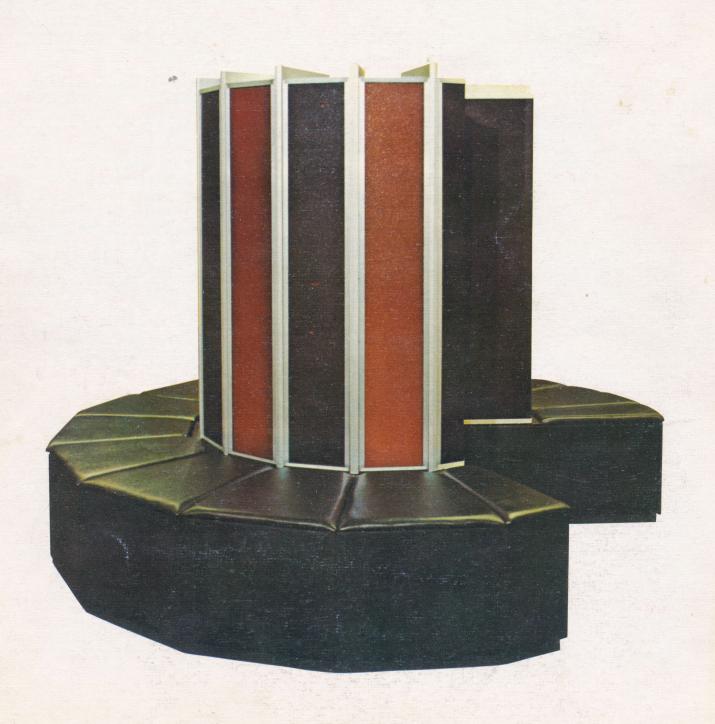

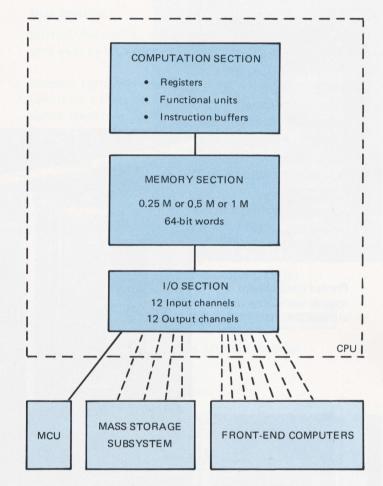

The basic configuration of the CRAY-1 consists of the central processor unit (CPU), power and cooling equipment, one or more minicomputer consoles, and a mass storage (disk) subsystem. The CPU holds the computation, memory, and I/O sections of the computer. A minicomputer serves either as a maintenance control unit or a job entry station.

#### INPUT/OUTPUT

are input and twelve output. Any number of channels may be active at a given time. For a 16-bit channel, transfer rates of 160 million bits per second can be achieved. Higher rates are possible but in practice, the maximum transfer rate is limited by the speed of peripheral devices.

Input/output is via twenty-four I/O channels, twelve of which

BASIC COMPUTER SYSTEM

Input/output and the CPU share memory access via a single port. I/O priority is sufficient to ensure maintaining the required transfer rates for the peripheral devices.

#### **MEMORY**

The CRAY-1 memory is constructed of 1024-bit LSI chips. Up to 1,048,576 (generally referred to as one million) 72-bit words are arranged in 16 banks. Up to 524,288 words can be arranged in 8 banks. A word consists of 64 data bits and 8 check bits. The bank cycle time, that is, the time required to remove or insert an element of data in memory, is 50 nanoseconds. This short cycle time provides an extremely efficient random-access memory. There is no inherent memory degradation for 16-bank memories with less than one million words of memory.

A single-error-correction double error detection (SECDED) network assures that data written into memory can be returned to the computation section with consistent precision. There are eight check bits per memory word.

#### **FACTS AND FIGURES**

| CPU                                       |                                         |  |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------|-----------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| Instruction size                          | 16 or 32 bits                           |  |  |  |  |  |  |  |  |  |  |  |

| Repertoire size                           | 128 instruction codes                   |  |  |  |  |  |  |  |  |  |  |  |

| Clock period                              | 12.5 nsec                               |  |  |  |  |  |  |  |  |  |  |  |

| Instruction stack/buffers                 | 64 words (4096 bits)                    |  |  |  |  |  |  |  |  |  |  |  |

| Functional units                          | twelve:                                 |  |  |  |  |  |  |  |  |  |  |  |

|                                           | 3 integer add 1 integer multiply        |  |  |  |  |  |  |  |  |  |  |  |

|                                           | 2 shift                                 |  |  |  |  |  |  |  |  |  |  |  |

|                                           | 2 logical<br>1 floating add             |  |  |  |  |  |  |  |  |  |  |  |

|                                           | 1 floating multiply                     |  |  |  |  |  |  |  |  |  |  |  |

|                                           | 1 reciprocal approx. 1 population count |  |  |  |  |  |  |  |  |  |  |  |

| Programmable registers                    | 8x64 64-bit                             |  |  |  |  |  |  |  |  |  |  |  |

| Trogrammable registers                    | 73 64-bit                               |  |  |  |  |  |  |  |  |  |  |  |

|                                           | 72 24-bit<br>1 7-bit                    |  |  |  |  |  |  |  |  |  |  |  |

| Max. vector result rate                   | 12.5 nsec / unit                        |  |  |  |  |  |  |  |  |  |  |  |

| wax. vector result rate                   | 12.3 11300 7 diffe                      |  |  |  |  |  |  |  |  |  |  |  |

| FLOATING POINT COMPUTA                    | ATION RATES (results per second)        |  |  |  |  |  |  |  |  |  |  |  |

| Addition                                  | 80 x 10 <sup>6</sup> / sec              |  |  |  |  |  |  |  |  |  |  |  |

| Multiplication                            | 80 x 10 <sup>6</sup> / sec              |  |  |  |  |  |  |  |  |  |  |  |

| Division                                  | 25 x 10 <sup>6</sup> / sec              |  |  |  |  |  |  |  |  |  |  |  |

| MEMORY                                    |                                         |  |  |  |  |  |  |  |  |  |  |  |

| Technology                                | bipolar semiconductor                   |  |  |  |  |  |  |  |  |  |  |  |

| Word length                               | 72 bits (64 data, 8 SECDED)             |  |  |  |  |  |  |  |  |  |  |  |

| Address space                             | 4M words                                |  |  |  |  |  |  |  |  |  |  |  |

| Data path width (bits)                    | 64 (1 word)                             |  |  |  |  |  |  |  |  |  |  |  |

| Cycle time                                | 50 nsec.                                |  |  |  |  |  |  |  |  |  |  |  |

| Size                                      | 262,144 words<br>or 524,288 words       |  |  |  |  |  |  |  |  |  |  |  |

|                                           | or 1,048,576 words                      |  |  |  |  |  |  |  |  |  |  |  |

| Organization / interleave                 | 16 banks (8 banks optional)             |  |  |  |  |  |  |  |  |  |  |  |

| Maximum band width                        | 80 x 10 <sup>6</sup> words / sec        |  |  |  |  |  |  |  |  |  |  |  |

|                                           | (5.1 x 10 <sup>9</sup> bits / sec)      |  |  |  |  |  |  |  |  |  |  |  |

| Error checking                            | SECDED                                  |  |  |  |  |  |  |  |  |  |  |  |

| PHYSICAL CHARACTERISTI                    | CS / ELECTRONIC TECHNOLOGY              |  |  |  |  |  |  |  |  |  |  |  |

| Size of CPU cabinet                       | 9 ft diameter base                      |  |  |  |  |  |  |  |  |  |  |  |

|                                           | 4.5 ft diameter center                  |  |  |  |  |  |  |  |  |  |  |  |

|                                           | 6.5 ft height                           |  |  |  |  |  |  |  |  |  |  |  |

| Weight of mainframe                       | 5.25 tons                               |  |  |  |  |  |  |  |  |  |  |  |

| Cooling                                   | Freon                                   |  |  |  |  |  |  |  |  |  |  |  |

| Plug-in modules                           | 1662                                    |  |  |  |  |  |  |  |  |  |  |  |

| Module types                              | 113                                     |  |  |  |  |  |  |  |  |  |  |  |

| PC boards                                 | 5 layer                                 |  |  |  |  |  |  |  |  |  |  |  |

| Circuitry (equivalent no. of transistors) | 2.5M                                    |  |  |  |  |  |  |  |  |  |  |  |

| Logic                                     | ECL, 1 nsec.                            |  |  |  |  |  |  |  |  |  |  |  |

| High-density logic                        | SSI                                     |  |  |  |  |  |  |  |  |  |  |  |

|                                           |                                         |  |  |  |  |  |  |  |  |  |  |  |

# **COMPUTATION SECTION**

The computation section as illustrated on page 4 is composed of instruction buffers, registers, and functional units which operate together to execute sequences of instructions.

#### Data structure

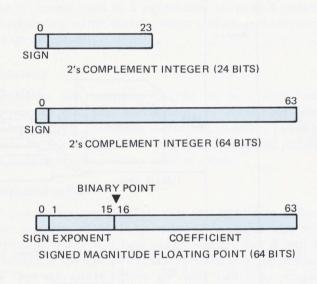

Internal character representation in the CRAY-1 is in ASCII with each 64-bit word able to accommodate eight characters.

Numeric representation is either in two's complement form (24-bit or 64-bit) or in 64-bit floating point form using a signed magnitude binary coefficient and a biased exponent. Exponent overflow and underflow is caused if the exponent is greater than  $57777_8$  or less than  $20000_8$ . Either of these conditions causes an interrupt except where the interrupt has been inhibited.

# **DATA FORMATS**

#### Instruction set

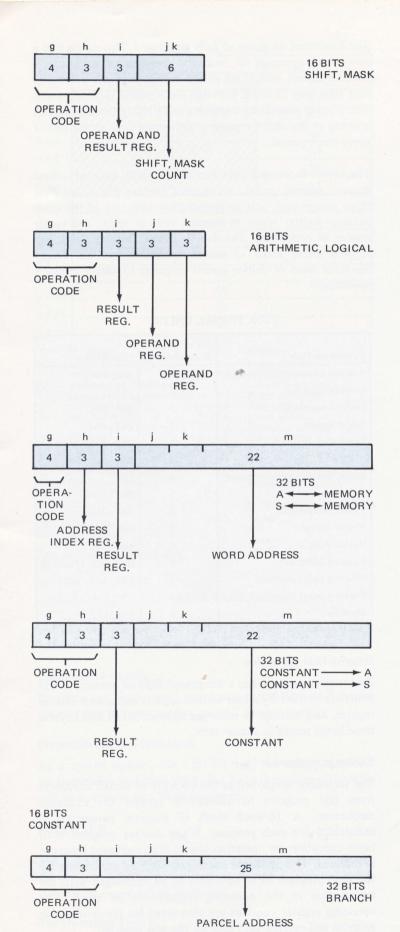

The CRAY-1 executes 128 operation codes as either 16-bit (one parcel) or 32-bit (two-parcel) instructions. Operation codes provide for both scalar and vector processing.

In general, an instruction that references registers occupies one parcel; an instruction that references memory occupies two parcels. All of the arithmetic and logical instructions reference registers.

Floating point instructions provide for addition, subtraction, multiplication, and reciprocal approximation. The reciprocal approximation instruction allows for the computation of a floating point divide operation using a multiple instruction sequence.

Integer or fixed point operations are provided for as follows: integer addition, integer subtraction, and integer multiplication. An integer multiply operation produces a 24-bit result; additions and subtractions produce either 24-bit or 64-bit results. No integer divide instruction is provided. The operation can be accomplished through a software algorithm using floating point hardware.

The instruction set includes Boolean operations for OR, AND, and exclusive OR and for a mask-controlled merge operation. Shift operations allow the manipulation of 64- or 128-bit operands to produce a 64-bit result. Similar 64-bit arithmetic capability is provided for both scalar and vector processing. Full indexing capability allows the programmer to index throughout memory in either scalar or vector modes of processing. This allows matrix operations in vector mode to be performed on rows, on columns, or on the diagonal.

Instructions for scalar population and leading zero counts return bit counts based on S register contents to an A register. Corresponding instructions for vector operations are available as a special option.

## Addressing

Instructions that reference data do so on a word basis. Instructions that alter the sequence of instructions being executed, that is, the branch instructions, reference parcels of words. In this case, the lower two bits of an address identify the location of an instruction parcel in a word.

#### Instruction buffers

All instructions are executed from four instruction buffers, each consisting of 64 16-bit registers. Associated with each instruction buffer is a base address register that is used to determine if the current instruction resides in a buffer. Since the four instruction buffers are large, substantial program segments can reside in them. Forward and backward branching within the buffers is possible and the program segments may be noncontiguous. When the current instruction does not reside in a buffer, one of the instruction buffers is filled from memory. Four memory words are transferred per clock period. The buffer that is filled is the one least recently filled, that is, the buffers are filled in rotation. To allow the current instruction to issue as soon as possible, the memory word containing the current instruction is among the first four transferred. A parcel counter register (P) points to the next parcel to exit from the buffers. Prior to issue, instruction parcels may be held in the next instruction parcel (NIP), lower instruction parcel (LIP) and current instruction parcel (CIP) registers.

# **Operating registers**

The CRAY-1 has five sets of registers, three primary and two intermediate. Primary registers can be accessed directly by functional units. Intermediate registers are not accessible by functional units but act as buffers between primary registers and memory.

The figure on page 4 represents the CRAY-1 registers and functional units. The 64 address and 64 scalar intermediate registers can be filled by block transfers from memory. Their purpose is to reduce memory references made by the scalar and address registers.

The eight address registers are each 24 bits and can be used to count loops, provide shift counts, and act as index registers in addition to their main use for memory references.

The eight 64-bit scalar registers in addition to contributing operands and receiving results for scalar operations can provide one operand for vector operations.

Each of the eight vector (V) registers is actually a set of 64 64-bit registers, called elements. The number of vector operations to be performed (that is, the vector length) determines how many of the elements of a register are used to supply operands in a vector set or receive results of the vector operation. The hardware accommodates vectors with lengths up to 64; longer vectors are handled by the software dividing the vector into 64-element segments and a remainder.

Associated with the vector registers are a 7-bit vector length register and a 64-bit vector mask register. The vector length register, as its name implies, determines the number of operations performed by a vector instruction. Each bit of the vector mask register corresponds to an element of a V register. The mask is used with vector merge and test instructions to allow operations to be performed on individual vector elements.

#### Supporting registers

In addition to the operating registers, the CPU contains a variety of auxiliary and control registers. For example, there is a channel address (CA) register and a channel limit register (CL) for each I/O channel.

#### **Functional units**

Instructions other than simple transmits or control operations are performed by hardware organizations known as functional units. Each of the twelve units in the CRAY-1 executes an algorithm or a portion of the instruction set. Units are independent. A number of functional units can be in operation at one time.

A functional unit receives operands from registers and delivers the result to a register when the function has been performed. The units operate essentially in three-address mode with source and destination addressing limited to register designators.

All functional units perform their algorithms in a fixed amount of time. No delays are possible once the operands have been delivered to the unit. The amount of time required from delivery of the operands to the unit to the completion of the calculation is termed the "functional unit time" and is measured in 12.5 nsec clock periods.

The functional units are all fully segmented. This means that a new set of operands for unrelated computation may enter a functional unit each clock period even though the functional unit time may be more than one clock period. This segmentation is made possible by capturing and holding the information arriving at the unit or moving within the unit at the end of every clock period.

The twelve functional units can be arbitrarily assigned to four groups: address, scalar, vector, and floating point. The first three groups each acts in conjunction with one of the three primary register types, to support address, scalar, and vector modes of processing. The fourth group, floating point, can support either scalar or vector operations and will accept operands from or deliver results to scalar or vector registers accordingly.

#### **FUNCTIONAL UNITS**

| Functional Unit               | Unit Time<br>(Clock Periods) | Instructions         |

|-------------------------------|------------------------------|----------------------|

| Address integer add           | 2                            | 030, 031             |

| Address multiply              | 6                            | 032                  |

| Scalar integer add            | 3                            | 060, 061             |

| Scalar logical                | 1                            | 042 - 051            |

| Scalar shift                  | 2                            | 052 - 055            |

|                               | 3                            | 056, 057             |

| Scalar leading zero/pop count | 4                            | 026                  |

|                               | 3                            | 027                  |

| Vector integer add            | 3                            | 154 - 157            |

| Vector logical                | 2                            | 140 - 147, 175       |

| Vector shift                  | 4                            | 150 - 153            |

| Floating point add            | 6                            | 062, 063, 170 - 173  |

| Floating point multiply       | 7                            | 064 - 067, 160 - 167 |

| Floating point reciprocal     | 14                           | 070, 174             |

| Memory                        | 7                            | 176, 177             |

# Memory field protection

Each object program has a designated field of memory. Field limits are defined by a base address register and a-limit address register. Any attempt to reference instructions or data beyond these limits results in a range error.

# Exchange mechanism

The technique employed in the CRAY-1 to switch execution from one program to another is termed the exchange mechanism. A 16-word block of program parameters is maintained for each program. When another program is to begin execution, an operation known as an exchange sequence is initiated. This sequence causes the program parameters for the next program to be executed to be exchanged with the information in the operating registers to be saved. The operating register contents are thus saved for the terminating program and entered with data for the new program.

Exchange sequences may be initiated automatically upon occurrence of an interrupt condition or may be voluntarily

means of expressing symbolically all hardware functions of the CPU. Augmenting the instruction repertoire is a set of versatile pseudo instructions that provide users with options for generating macro instructions, organizing programs, and so on.

CAL enables the user to tailor programs to the architecture of the CRAY-1. The operating system as well as most other software provided by Cray Research, Inc. is coded in CAL assembly language.

#### Source program maintenance

An UPDATE program provides a means of maintaining source language programs as card images on mass storage or on magnetic tape. The user converts the source language program to a data set called a library in which each of the original cards is assigned a number. Later, when the user wishes to modify the card, it is referenced by its number and is accordingly deleted, replaced, or used for an insertion point of additional

# CRAY-1 INSTRUCTION SET

| ** | Logical differences of (Sj) and (Vk) to Vi |        | VM Transmit (Sj) if VM bit = 1; (Vk) if $VM$ bit = 0 + 0 Vi |                          | VM          |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Shift (Vj) right (Ak) places to Vi | Shift (Vj) right one place to Vi | cAk Double shift (Vj) left (Ak) places to Vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Double shift                           |           | 1                                      | Integer sums of (Vi) and (Vk) to Vi | Integer differences                |                                                          |                                  |                                           |                                           | k Half precision rounded floating products of (Sj) and (Vk) to Vi |                                                                                     |        |                                      | (VK) to V1                               | k=2 - floating products of (Sj) and (Vk) to Vi | k=2 - floating products of $(Vj)$ and $(Vk)$ to $Vi$ | F108                                       | Normalize (Vk) to Vi               |        | Floating differences of (Sj) and (Vk) | Transmit normalized negatives of (Vk) to |               | Floating reciprocal approximations of $(V_j)$ to $V_i$ | VM=1 where $(Vj)=0$       | $VM=1$ where $(Vj) \neq 0$ | where (Vj)                                                                                                                                     | VM=1 where (Vj) negative  | k Read (VL) words to Vi from (A0) incremented by (Ak) |                                           | incremented by 1 | Store (VL) words from Vj to (A0) incremented by (Ak) | Store (VL) words from Vj to (A0)                                                |     |  |

|----|--------------------------------------------|--------|-------------------------------------------------------------|--------------------------|-------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------|----------------------------------------|-------------------------------------|------------------------------------|----------------------------------------------------------|----------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------|--------------------------------------|------------------------------------------|------------------------------------------------|------------------------------------------------------|--------------------------------------------|------------------------------------|--------|---------------------------------------|------------------------------------------|---------------|--------------------------------------------------------|---------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------|-------------------------------------------|------------------|------------------------------------------------------|---------------------------------------------------------------------------------|-----|--|

|    | Sj\Vk                                      | Vj\Vk  | Sj:Vk&VM                                                    | #VM&Vk                   | Vj:Vk&VM    | Vicab                                      | Vj <1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Vj>Ak                              | Vj>1                             | Vj,Vj <ak< td=""><td>Vj, Vj&lt;1</td><td>Vj,Vj&gt;Ak</td><td>Vj,Vj&gt;1</td><td>Sj+VK</td><td>Si-Vk</td><td>-Vk</td><td>Vj-Vk</td><td>Sj*FVk</td><td>Vj*FVk</td><td>Sj*HVk</td><td>Vj*HVk</td><td>Sj*RVk</td><td>Vj*RVk</td><td>•</td><td>Sj*IVk</td><td>Vj*IVk</td><td>Sj+FVk</td><td>+FVk</td><td>Vj+FVk</td><td>Sj-FVk</td><td>- FVk</td><td>Vj-FVK</td><td>/HVj</td><td>Vj,Z</td><td>Vj,N</td><td>Vj,P</td><td>Vj,M</td><td>, A0, Ak</td><td>,A0,1</td><td></td><td>Vj</td><td>Vj</td><td></td><td></td></ak<> | Vj, Vj<1                               | Vj,Vj>Ak  | Vj,Vj>1                                | Sj+VK                               | Si-Vk                              | -Vk                                                      | Vj-Vk                            | Sj*FVk                                    | Vj*FVk                                    | Sj*HVk                                                            | Vj*HVk                                                                              | Sj*RVk | Vj*RVk                               | •                                        | Sj*IVk                                         | Vj*IVk                                               | Sj+FVk                                     | +FVk                               | Vj+FVk | Sj-FVk                                | - FVk                                    | Vj-FVK        | /HVj                                                   | Vj,Z                      | Vj,N                       | Vj,P                                                                                                                                           | Vj,M                      | , A0, Ak                                              | ,A0,1                                     |                  | Vj                                                   | Vj                                                                              |     |  |

|    | Vi                                         | Vi     | Vi                                                          | Vi                       | Vi          | Λ;                                         | ٧i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Vi                                 | Vi                               | Vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Vi                                     | Vi        | Vi                                     | V1<br>V:                            | ۷۱:                                | Vi                                                       | Vi                               | Vi                                        | Vi                                        | Vi                                                                | Vi                                                                                  | Vi     | Vi                                   | ;                                        | Vi                                             | Vi                                                   | Vi                                         | Vi                                 | Vi     | Vi                                    | Vi                                       | Vi            | Vi                                                     | VM                        | VM                         | VM                                                                                                                                             | VM                        | Vi                                                    | Vi                                        |                  | ,A0,Ak                                               | ,A0,1                                                                           |     |  |

|    | 144ijk                                     | 145ijk | 146ijk                                                      | +146i0k                  | 147 i j k   | 15031                                      | 150110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 151ijk                             | +151ij0                          | 152ijk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | +152ij0                                | 153ijk    | 1531j0                                 | 154ijk                              | 15611k                             | +156i0k                                                  | 157ijk                           | 160ijk                                    | 161ijk                                    | 162ijk                                                            | 163ijk                                                                              | 164ijk | 165ijk                               |                                          | 166ijk                                         | 167ijk                                               | 170ijk                                     | +170i0k                            | 171ijk | 172ijk                                | +172i0k                                  | 173ijk        | 174ijx                                                 | 175xj0                    | 175xj1                     | 175xj2                                                                                                                                         | 175xj3                    | 176ixk                                                | +176ix0                                   |                  | 177xjk                                               | +177xj0                                                                         |     |  |

| *  | Store (Ai) words at B register jk to (A0)  |        | register jk from                                            | at T register jk to (A0) |             | Transmit exp = 1's complement of jkm to Si | ask exp = 64-jk bits in Si from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Form 1's mask exp = jk bits in Si from | Clear Si  | Logical product of (Sj) and (Sk) to Si | Sign bit of (Sj) to Si              | Sign bit of (Sj) to Si $(j\neq 0)$ | Logical product of (Sj) and 1's complement of (Sk) to Si | (Sj) with sign bit cleared to Si | Logical difference of (Sj) and (Sk) to Si | Toggle sign bit of Sj, then enter into Si | ij, t                                                             | Logical equivalence of (SK) and (SJ) to Si<br>Transmit 1's complement of (Sk) to Si |        | Logical equivalence of (Sj) and sign | Enter 1's complement of sign hit into Si | Logical product of (Si)                        | ORed with logical product                            | Scalar merge of (SI) and sign bit of to Si | Logical sum of (Sj) and (Sk) to Si |        | and sign bit to Si                    | d sign bit to Si (j≠0)                   | sign bit into | Shift (Si) left exp = jk places to S0                  | (Si) left evn = ik nlaces |                            | Shift (Si and Sj) left                                                                                                                         | Shift (Si and Sj) left of | (Si) lef                                              | Shift (Sj and Si) right (Ak) places to Si | to Si            |                                                      | Integer sum of (5j) and (5k) to Si<br>Integer difference of (Si) and (Sk) to Si |     |  |

| 1  | Bjk, Ai                                    | , A0   |                                                             | Tjk, Ai                  | IJK, AI     | exp                                        | <exp< td=""><td>#&gt;exp</td><td>1</td><td>-1</td><td>&gt;exp</td><td>0</td><td>SjęSk</td><td>SjęSB</td><td>SB&amp;Sj</td><td>#SkgSj</td><td>#SB&amp;Sj</td><td>Sj\sk</td><td>Sj\SB</td><td>SB\Sj</td><td>#5J\5K<br/>#SK</td><td>#Sj\SB</td><td>#SB\Sj</td><td>#<br/>%</td><td>Si!Si&amp;Sk</td><td>00:01:0</td><td>5]:51456</td><td>Sj:Sk</td><td>Sk</td><td>Sj;SB</td><td>SB:Sj</td><td>SB</td><td>Sicexp</td><td>Siebyn</td><td>Sivexp</td><td>Si,Sj<ak< td=""><td>Si, Sj&lt;1</td><td>SicAk</td><td>Sj,Si Ak</td><td>Sj,Si&gt;1</td><td>SirAk</td><td>Sj+5k</td><td>-Sk</td><td></td></ak<></td></exp<> | #>exp                              | 1                                | -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | >exp                                   | 0         | SjęSk                                  | SjęSB                               | SB&Sj                              | #SkgSj                                                   | #SB&Sj                           | Sj\sk                                     | Sj\SB                                     | SB\Sj                                                             | #5J\5K<br>#SK                                                                       | #Sj\SB | #SB\Sj                               | #<br>%                                   | Si!Si&Sk                                       | 00:01:0                                              | 5]:51456                                   | Sj:Sk                              | Sk     | Sj;SB                                 | SB:Sj                                    | SB            | Sicexp                                                 | Siebyn                    | Sivexp                     | Si,Sj <ak< td=""><td>Si, Sj&lt;1</td><td>SicAk</td><td>Sj,Si Ak</td><td>Sj,Si&gt;1</td><td>SirAk</td><td>Sj+5k</td><td>-Sk</td><td></td></ak<> | Si, Sj<1                  | SicAk                                                 | Sj,Si Ak                                  | Sj,Si>1          | SirAk                                                | Sj+5k                                                                           | -Sk |  |

|    | 035ijk 0,A0                                |        |                                                             |                          | 05/1jk 0,A0 | 041ijkm (Si                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 043ijk Si                              | 043i00 Si |                                        | .044ij0 Si                          |                                    | 045ijk Si                                                | 045ij0 Si                        | 046ijk Si                                 | 046ij0 Si                                 |                                                                   | 047i0k Si                                                                           |        | 047ij0 Si                            | 047:00 Si                                |                                                |                                                      | 050130 51                                  | 051ijk Si                          |        | 051ij0 Si                             |                                          |               | 052ijk S0                                              |                           |                            |                                                                                                                                                |                           |                                                       |                                           |                  | 1057i0k Si                                           | U6U1jk Si                                                                       |     |  |

<sup>†</sup> Special CAL syntax format