# SYSTEM OVERVIEW

5101 ONWARDS.

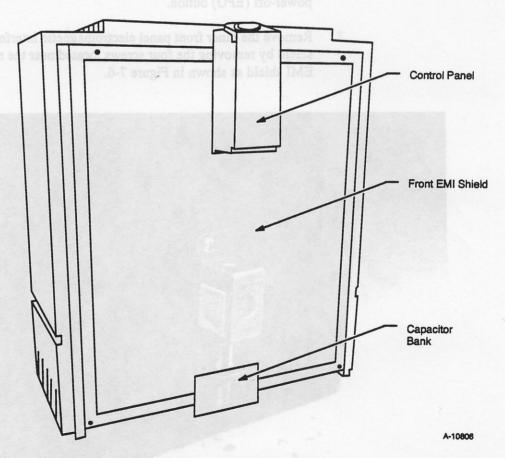

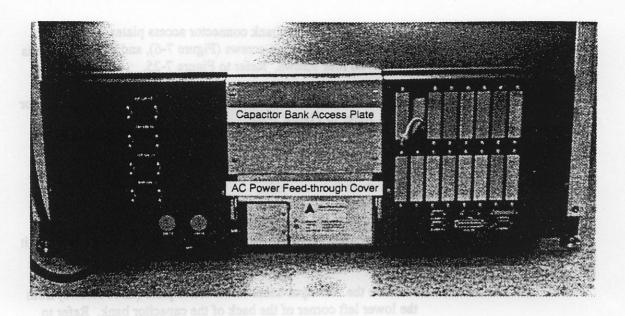

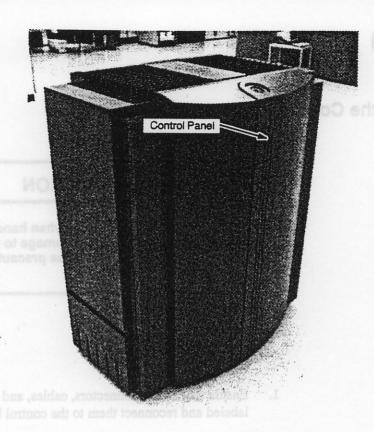

The CRAY Y-MP EL computer system is a completely self-contained system. This means that the central processing unit (CPU), input/output subsystem (IOS), and all peripherals can be contained in one cabinet. The cabinet can be installed easily in most general office environments equipped with a 200- to 250-Vac power source. (47-63 Hg) 30 Amp/phase

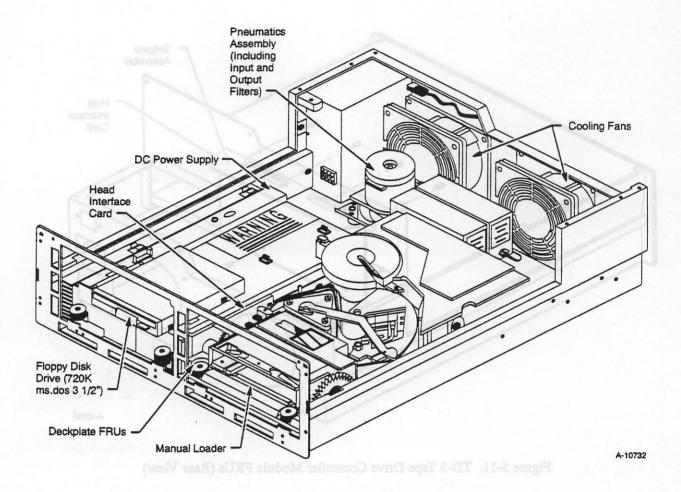

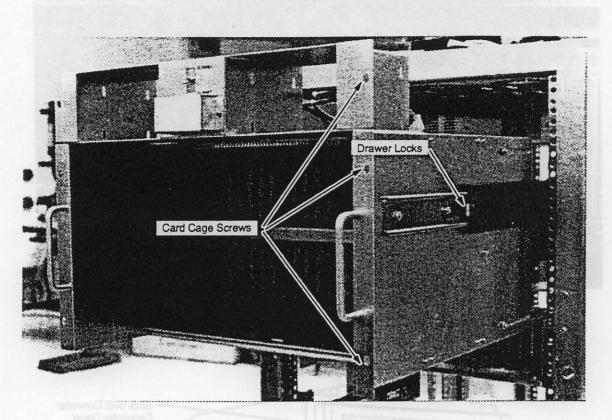

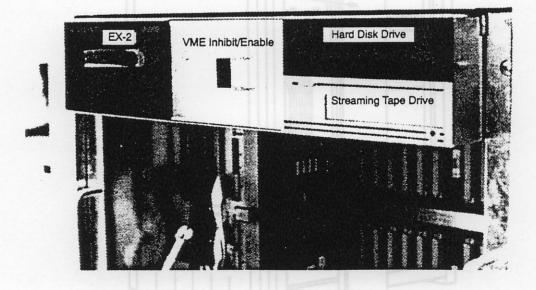

One to four CPU boards can be installed in the CRAY Y-MP EL primary cabinet. This cabinet also holds four memory boards, an IOS constructed from a Versabus Modular Eurocard (VMEbus)-based assembly, and the optional peripherals as requested by the customer. Another component in the primary cabinet is the small computer system interface (SCSI) subsystem. The SCSI subsystem consists of a cartridge-type streaming tape drive, a 780-Mbyte hard disk drive, and an 8-mm helical scan tape drive. The SCSI tape drives are used to install any new releases of software as they become available. It can also perform data transfers and is the system backup and boot device.

The primary cabinet is designed so that another standard cabinet can be bolted to the primary cabinet to expand the system. It is possible to connect as many as three expansion cabinets to the primary cabinet, allowing for IOS and peripheral expansion.

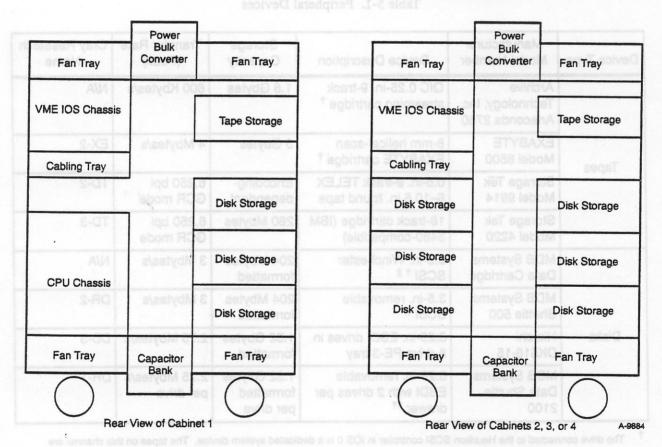

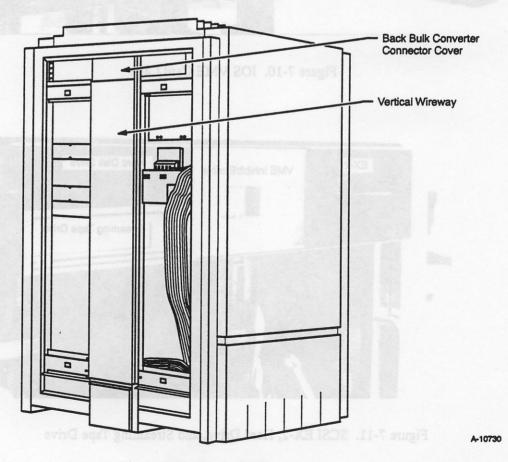

Figure 1-1 shows how three expansion cabinets are configured with the CRAY Y-MP EL system. Figure 1-2 shows a two-cabinet CRAY Y-MP EL system.

|                    | Conf. None Sept.       | N. V. Samora Ca.       |                        |

|--------------------|------------------------|------------------------|------------------------|

|                    | stryttad ara c         |                        |                        |

| Primary<br>Cabinet | Expansion<br>Cabinet 1 | Expansion<br>Cabinet 2 | Expansion<br>Cabinet 3 |

|                    | relientees l           | · ης.                  |                        |

Figure 1-1. Left Side View (Maximum Configuration)

Figure 1-2. CRAY Y-MP EL Computer System

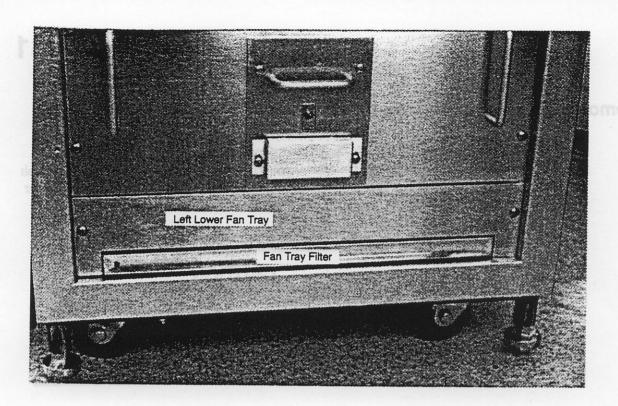

All of the cabinets forming the CRAY Y-MP EL system are air cooled by integrated fans at both the top and bottom of the frame. This form of cooling is referred to as vertical cooling.

The peripheral devices available on the CRAY Y-MP EL system and their characteristics are listed below.

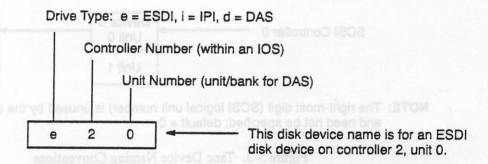

#### Disk units

- DD-3 low-performance disk unit

- 1.5 Gbytes; 5.25 inch ESDI drive

- 2.75-Mbyte/s transfer rate

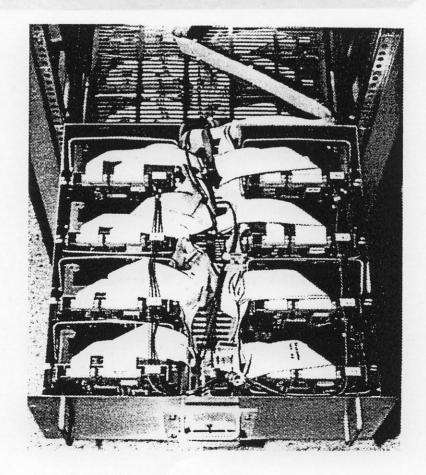

- Packaged eight drives per drawer with a shared power supply

- DC-3 controller

- Controls up to four enhanced serial drive interface (ESDI) disk drives (CIPRICO RF-3411)

- Each disk controller provides error correction code (ECC) and media defect management

- DD-4 medium-performance disk unit

- 3.0 Gbyte 8-inch two-head intelligent peripheral interface (IPI) dual port disk drive

- 9.34 Mbytes/s transfer rate

- Packaged two disk drives per drawer with one power supply per drive

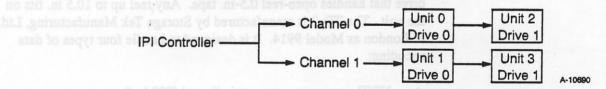

- DC-4 controller controls IPI-2 containing two IPI channels;

each channel can handle two DD-4 disk drives

- DAS-2 disk array subsystem

- Intelligent disk array controller (bus master by Maximum Strategy, Inc.)

- Bank of eight 1.5-Gbyte ESDIs for storage, plus one for parity and one spare

- Hardware striping used to distribute data evenly across all drives

- Sustained transfer rate of 13 Mbytes/s

- Has 12-Gbyte unformatted capacity

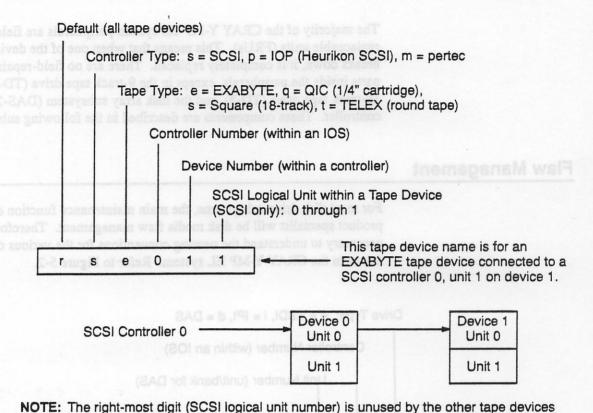

#### Tape units

- 9-track tape drive subsystem

- One TCU-2 tape controller unit (CIPRICO TM-3000)

- One TD-2 800 bpi (NRZI), 1600 bpi (PE), 6250 bpi (GCR)

9-track low profile tape drive, 125 ips

- Cartridge tape drive (EXABYTE) models RST 1

- EX-1 2.3 Gbyte, EXB-8200 246K/s 8-mm tape drive

- EX-2 5.0 Gbyte, EXB-8500 500K/s 8-mm tape drive

- TD-3 0.5-inch cartridge tape drive; 3480-compatible tape

- One SCSI peripheral controller (SI-1)

- One 18-track tape drive in low-profile configuration

- DR-1 removable disk system

- Dual 5.25-inch disks in easily removable cartridges designed to protect data from damage during transport

- DR-2 removable IOS disk drive

Customers select peripheral devices according to their requirements.

## **CPU Overview**

The CPU in the CRAY Y-MP EL computer system is located on a single 16 x 22 inch printed circuit (PC) board. This PC board contains all of the logic associated with the CRAY Y-MP EL system CPU. Very large scale integration (VLSI) solid-state technology enables a relatively small PC board to contain an entire CPU.

The VLSI chips used in the CPU are application-specific integrated circuits (ASICs). They are constructed using complementary metal oxide semiconductors (CMOS). The ASICs are available in a single package size with 299 pins. The internal construction of the ASIC consists of 100,000 undefined gates. This massive number of gates is contained in a 2 x 2 inch package, which consumes an average of 5 watts at + 5 volts.

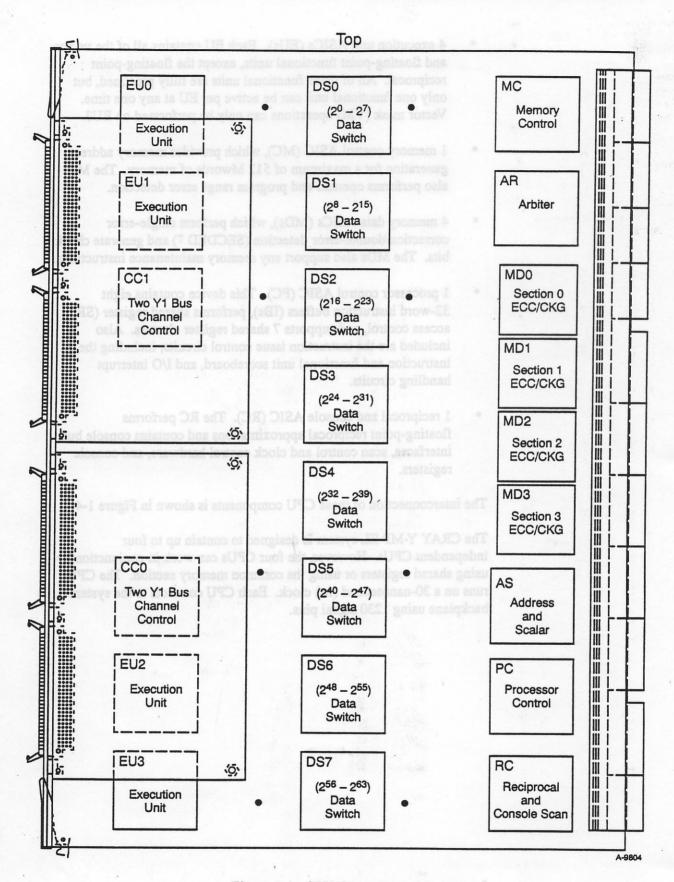

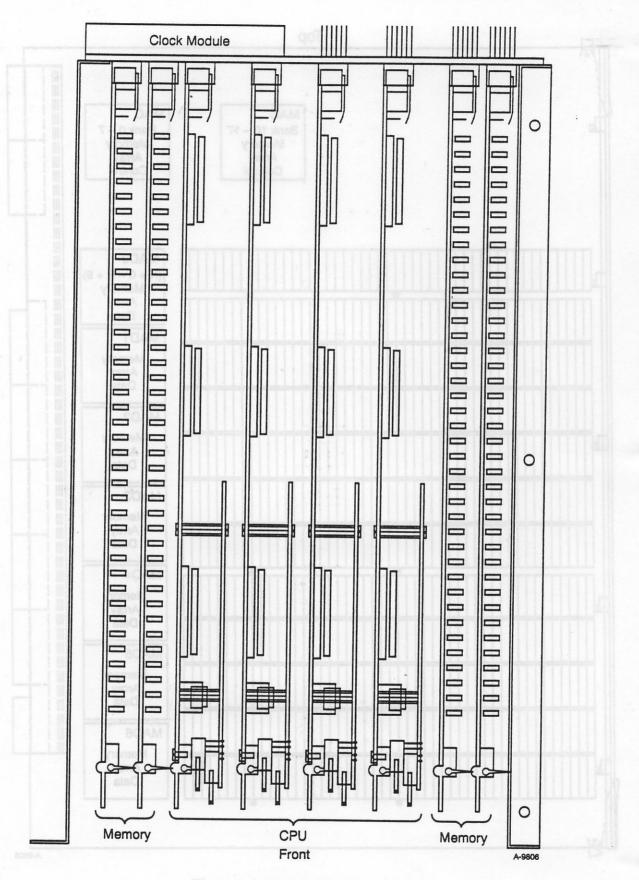

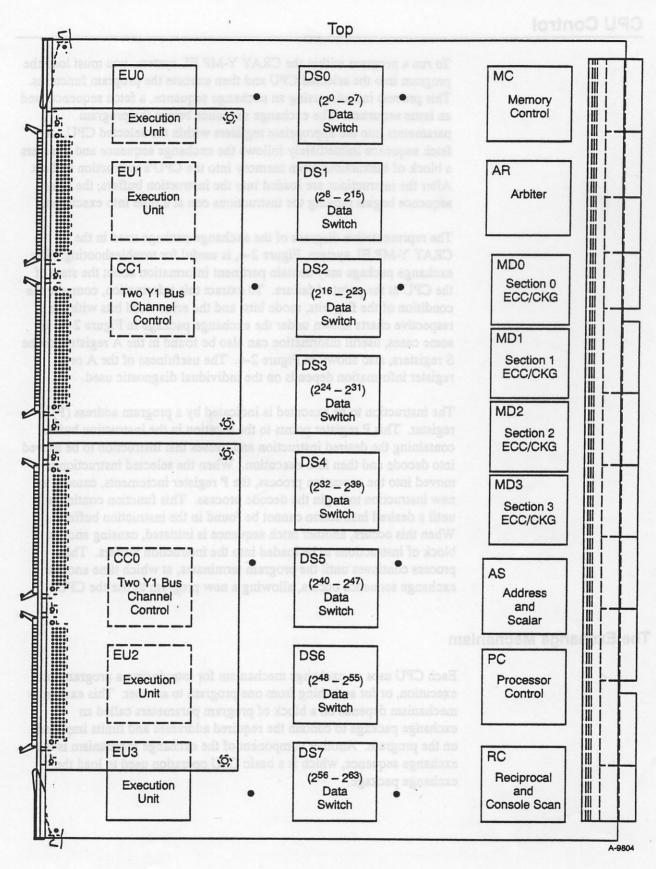

The CPU contains 23 separate ASICs consisting of nine application types. Figure 1-3 shows the chip layout for the CPU board of the CRAY Y-MP EL system.

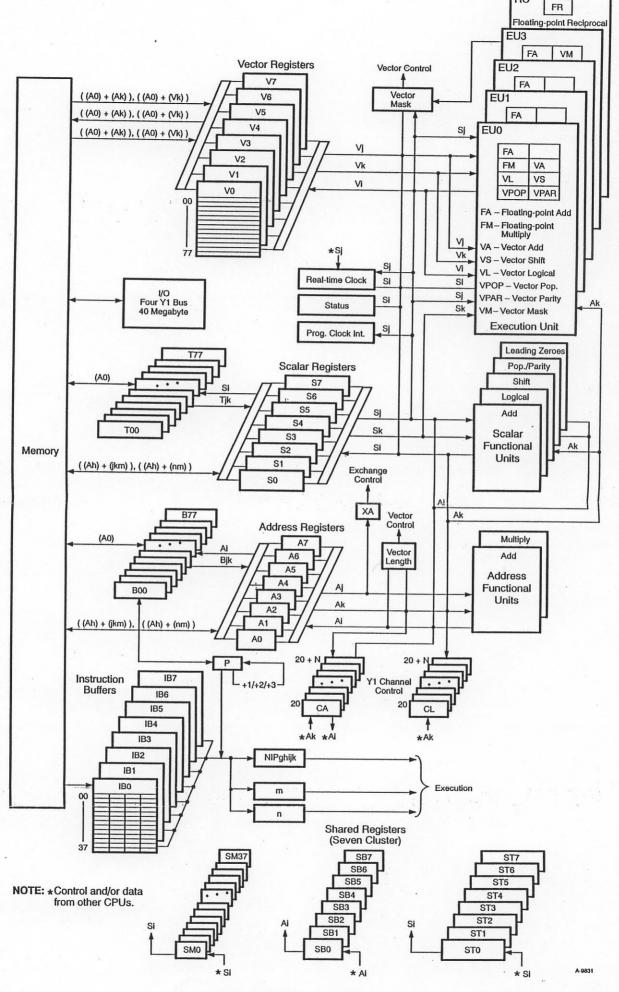

The nine types of ASICs that form the CPU are:

- 1 arbiter ASIC (AR), used for memory access control and for inter-CPU synchronization.

- 1 address and scalar ASIC (AS), containing the address registers, address functional units, scalar registers, and scalar functional units.

- 2 channel control ASICs (CCs). Each CC supports two Y1 channels, which are the 40-Mbyte/s channels that connect to the VMEbus subsystem. The CC is also used for control support.

- 8 data switch ASICs (DSs), which perform the major data steering between memory, channel, and functional units; they contain the vector registers and B/T registers.

- 4 execution unit ASICs (EUs). Each EU contains all of the vector and floating-point functional units, except the floating-point reciprocal. All of these functional units are fully pipelined, but only one functional unit can be active per EU at any one time. Vector mask (VM) operations can only be performed on EU3.

- 1 memory control ASIC (MC), which provides memory address generation for a maximum of 512 Mwords of memory. The MC also performs operand and program range error detection.

- 4 memory data ASICs (MDs), which perform single-error correction/double-error detection (SECDED †) and generate check bits. The MDs also support any memory maintenance instructions.

- 1 processor control ASIC (PC). This device contains eight 32-word instruction buffers (IBs), performs shared register (SR) access control, and supports 7 shared register clusters. Also included are the instruction issue control circuits, including the instruction and functional unit scoreboard, and I/O interrupt handling circuits.

- 1 reciprocal and console ASIC (RC). The RC performs floating-point reciprocal approximations and contains console bus interfaces, scan control and clock control hardware, and console registers.

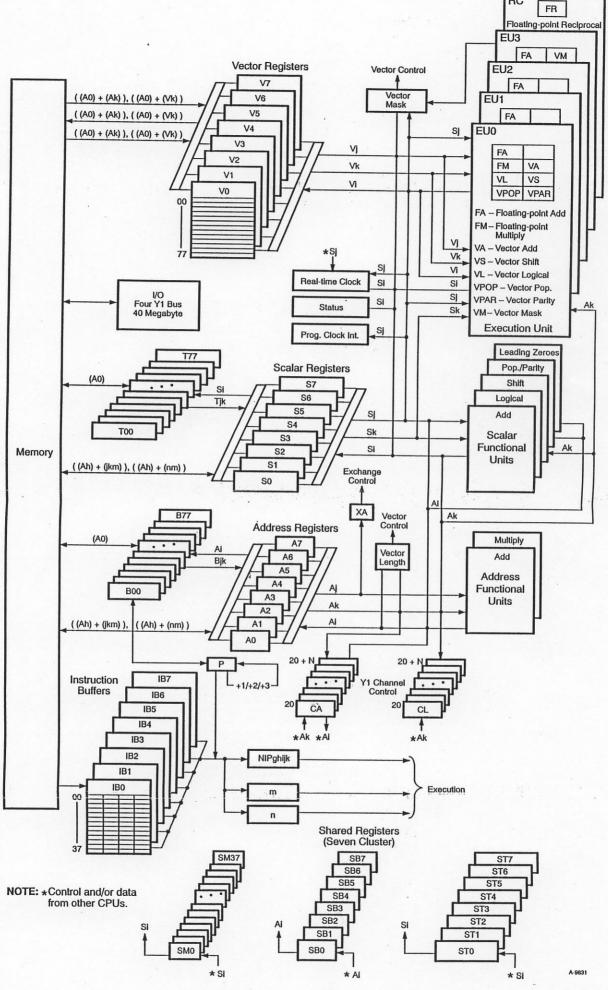

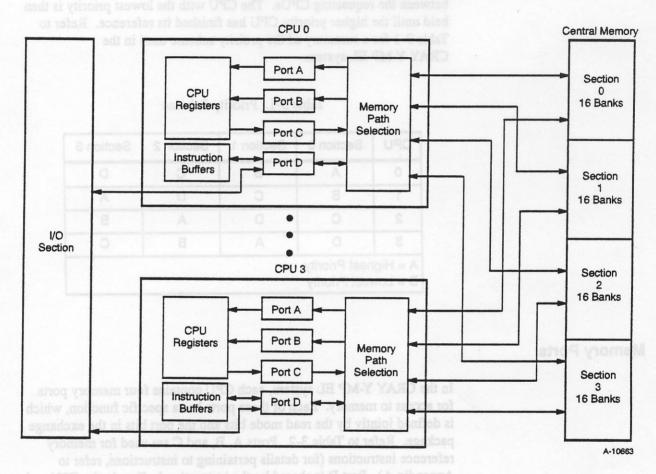

The interconnection of these CPU components is shown in Figure 1-4.

The CRAY Y-MP EL system is designed to contain up to four independent CPUs. However, the four CPUs can work in conjunction by using shared registers or using the common memory section. The CPU runs on a 30-nanosecond (ns) clock. Each CPU connects to the system backplane using 1230 signal pins.

<sup>†</sup> Hamming, R. W. "Error Detection and Correcting Codes." Bell System Technical Journal. 29.2 (1950): 147-160.

Figure 1-3. CPU/Channel Module

RC

Figure 1-4. CRAY Y-MP EL Block Diagram

# Blank Page

# **Memory Overview**

Central memory in the CRAY Y-MP EL system is contained on four PC boards. Each of these boards is 16 x 22 inches (the same size as the CPU board) and is composed of two ASIC types used for data control and fanout, with a total of nine ASICs per board and a specific number of 1M x 4 dynamic random access memory integrated circuits (DRAMs). The number of DRAMs depends upon the customer's choice of available memory options.

The CRAY Y-MP EL system can be ordered with a 32-Mword, a 64-Mword, or a 128-Mword central memory. In the case of the 32-Mword or 64-Mword options, the memory PC boards are half-populated modules. The difference between the 32-Mword and the 64-Mword memory options is that on the 32-Mword board, an address line is eliminated, effectively reducing the chip capacity. When the 32-Mword option is selected, a memory module contains 8 Mwords of memory supplied by 288 DRAMs. The 64 Mword memory option also contains 288 DRAMs, but provides 16 Mwords of memory per module. The third option, 128 Mword memory, is formed with 576 DRAMs per memory module, creating 32 Mwords per module. This 128-Mword option uses the full capacity of the memory module, and is considered to be fully populated.

The CRAY Y-MP EL system central memory contains a total of 64 banks spread across the four modules. Each module contains 16 banks and is considered a memory section. These 16 banks are separated into lower and upper banks on each board. Thus, a half-populated memory board uses only the lower bank, but still retains the full 16 banks of memory. This means that a fully populated memory module uses both upper and lower banks.

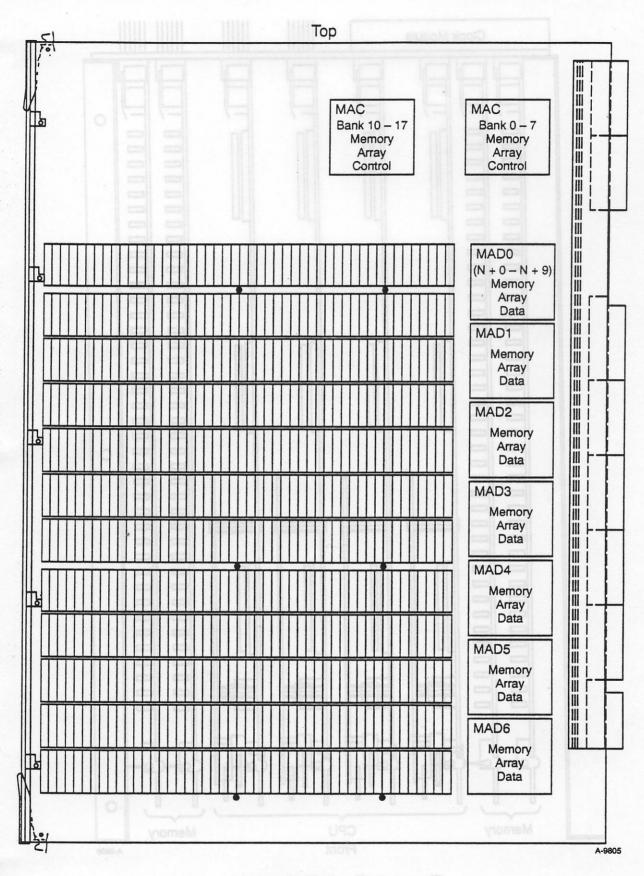

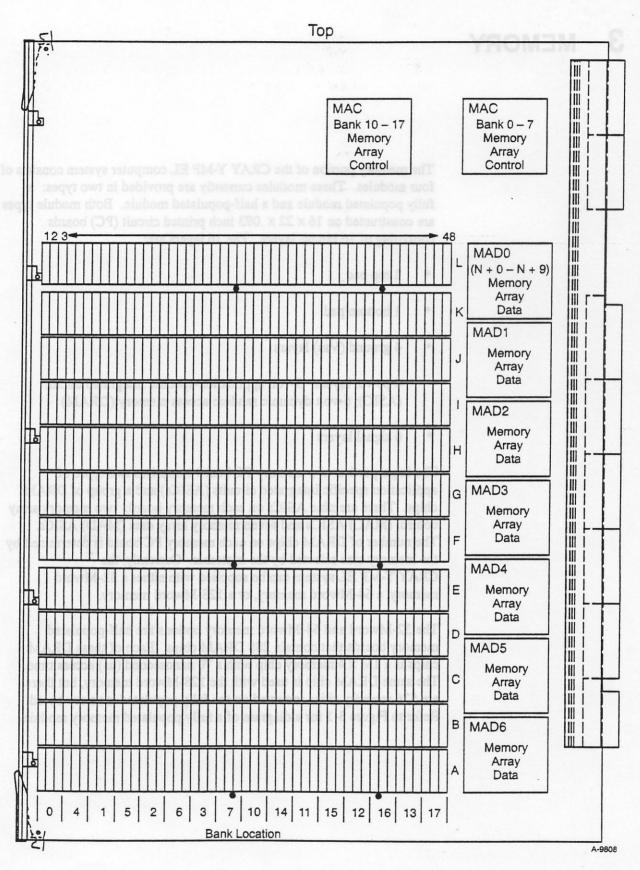

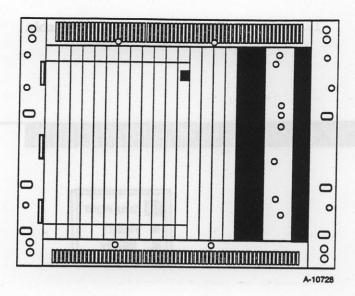

The layout of the memory board is shown in Figure 1-5. The two ASIC types used on the memory board are:

- 2 memory array control ASICs (MACs) support the four memory functions. These ASICs contain an address crossbar that allows access to memory from each of the four CPUs as well as refresh address counters for the local refresh function. The MACs also contain DRAM address and control circuitry, which provides control to all memory array data ASICs.

- 7 memory array data ASICs (MADs). These ASICs contain a data crossbar that connects the four CPUs to the 16 banks contained on each memory board. The MADs handle a portion of the 72-bit memory data word.

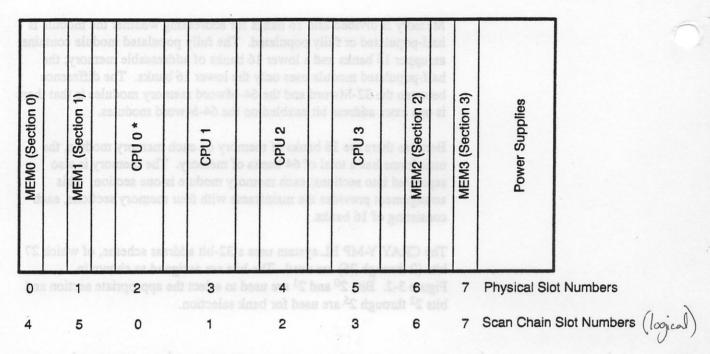

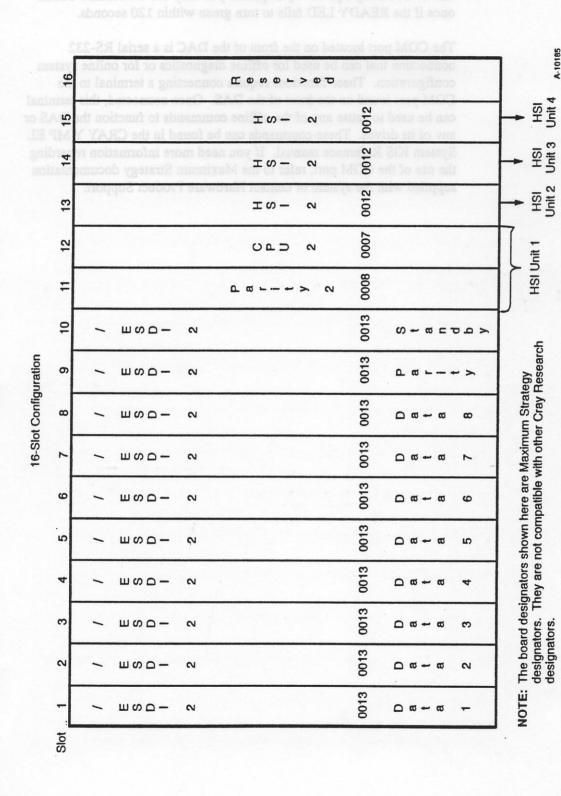

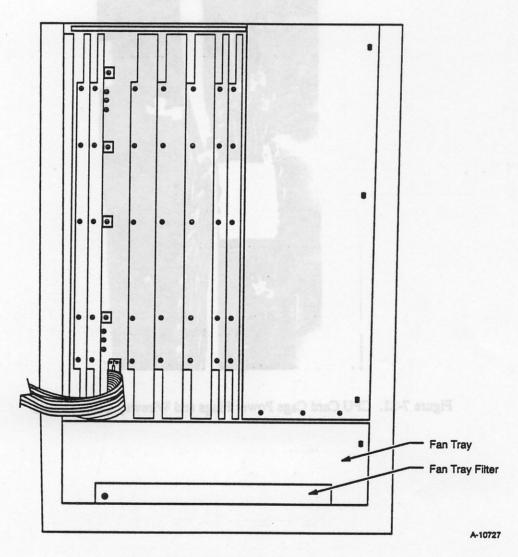

Figure 1-6 shows the chassis locations of the eight boards that form the CRAY Y-MP EL computer system. Note that this represents a top view, with the front of the chassis at the bottom of the diagram.

Figure 1-5. Memory Module

Figure 1-6. Chassis, Top View

# Input/Output Subsystem Overview

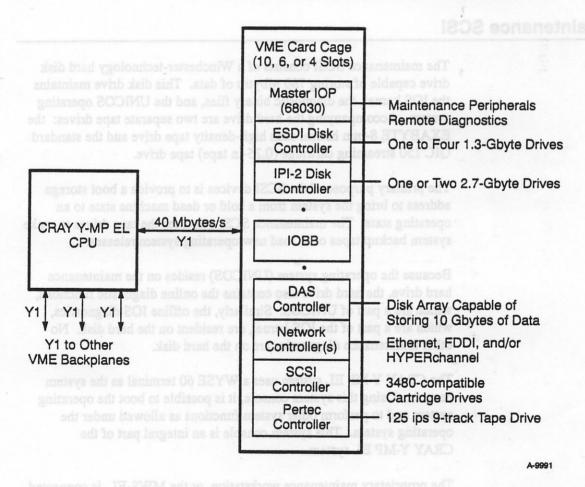

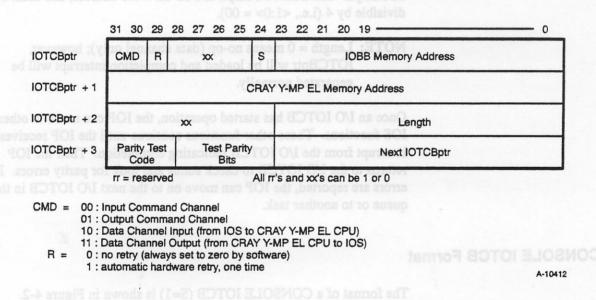

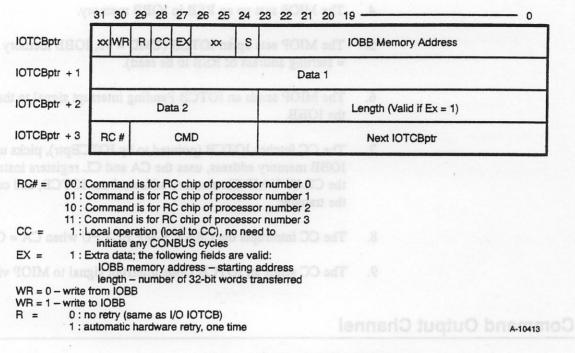

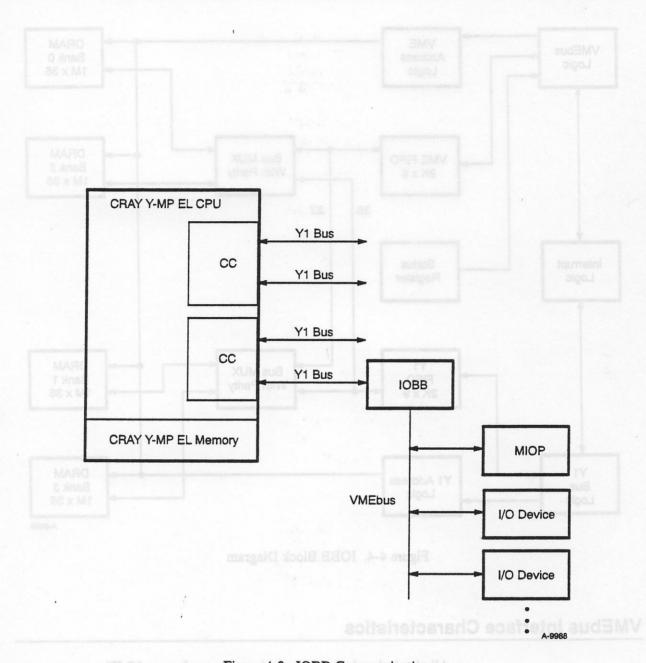

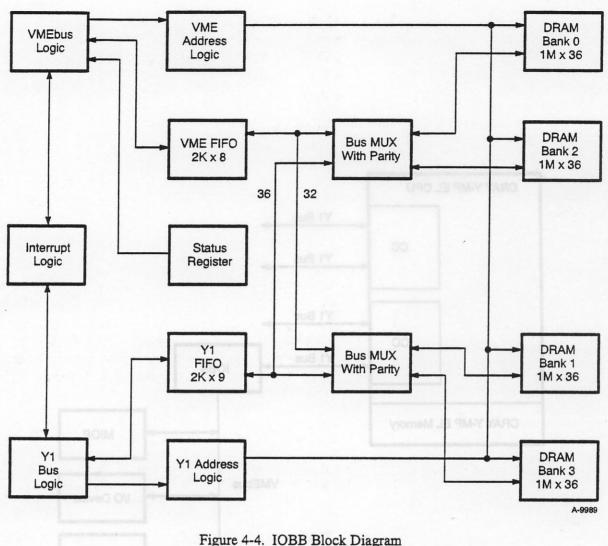

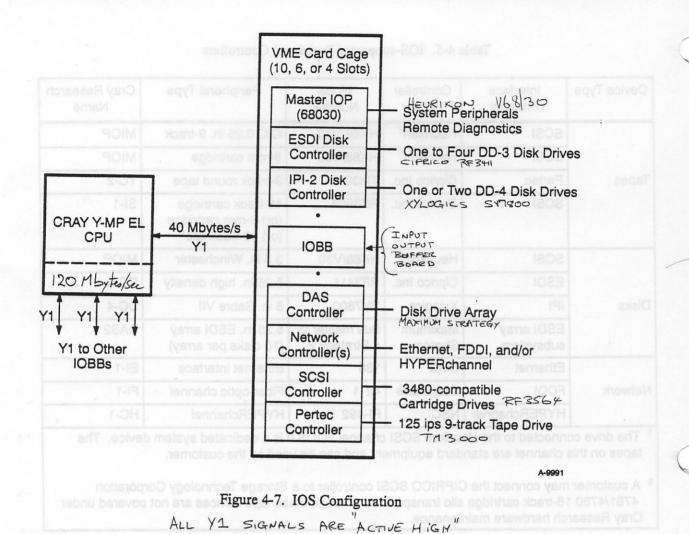

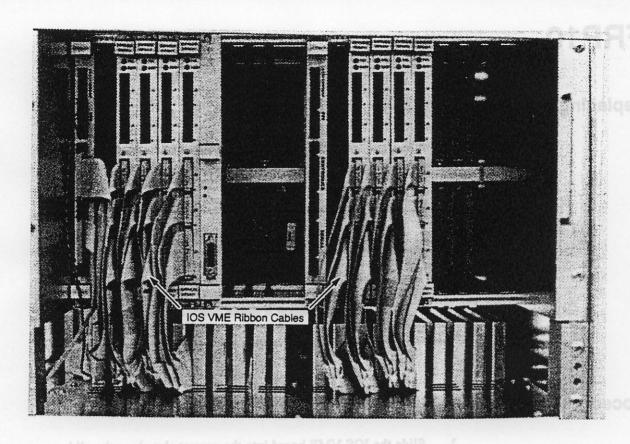

The IOS for the CRAY Y-MP EL system was selected to provide customers with the maximum choice of peripheral equipment. The IOS is a VME-based system that communicates with the CPU via the Y1 bus (a 40-Mbyte/s channel) connected to the input/output buffer board (IOBB). The IOBB is the only Cray Research, Inc. proprietary board within the IOS. All other functions within the IOS are performed using vendor-supplied VME boards.

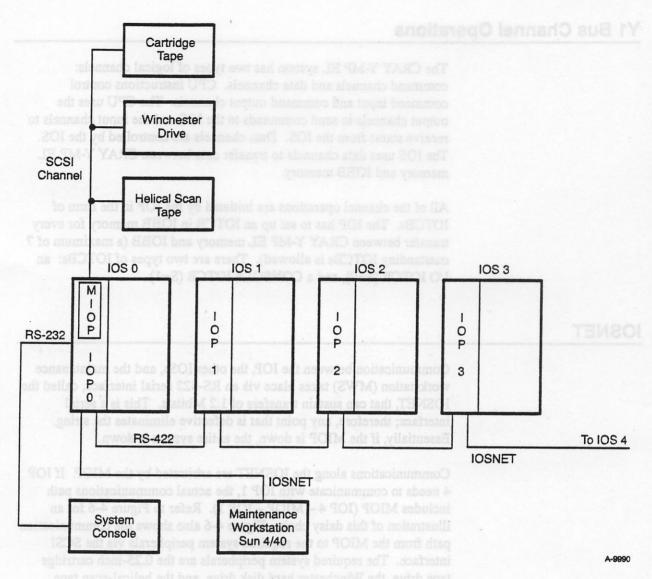

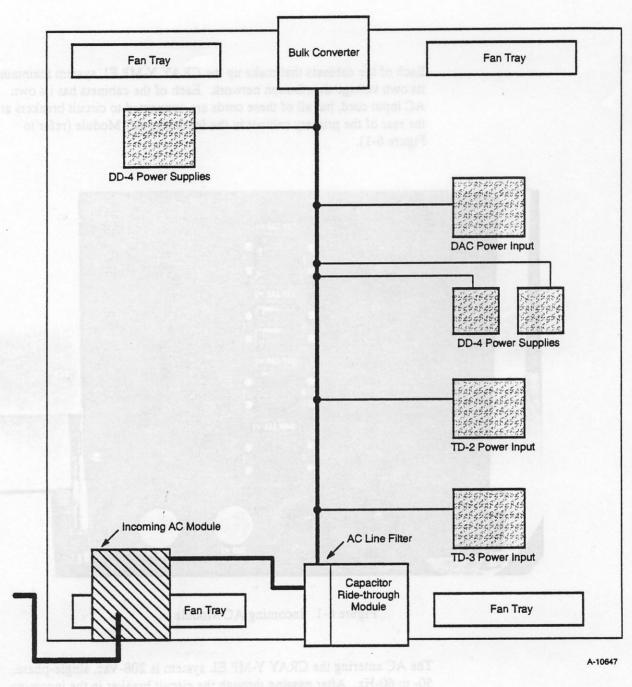

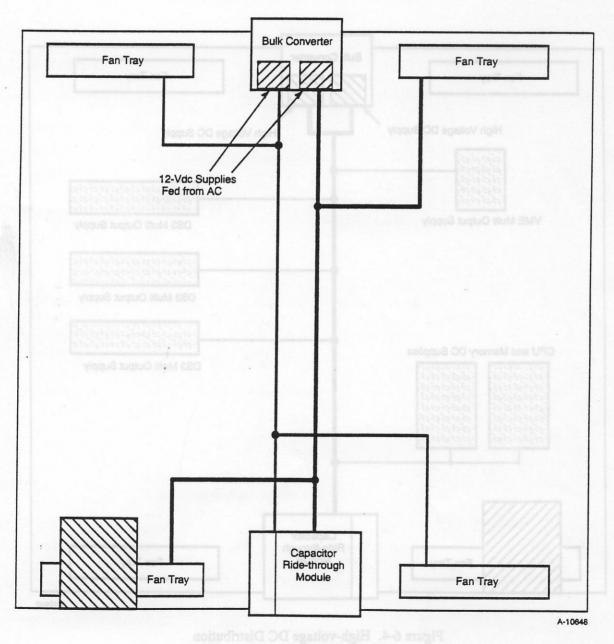

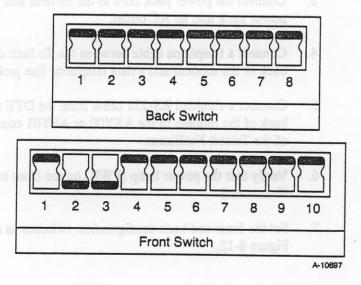

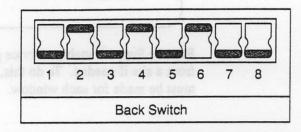

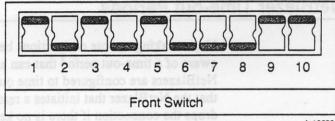

The restrictions of the IOS configuration require use of a 68030-type processor that is capable of processing 32 bits, and as many as eight peripheral controllers to handle data transfers. A possible IOS configuration is represented in Figure 1-7. The types of controllers used are defined by the customer's choice of system peripherals.

Figure 1-7. IOS Configuration

The standard VME mechanical chassis is a 19-inch rack mount chassis that is air cooled, supports standard 6U x 160 mm VME boards, and requires a 750-watt power supply. The backplane is a modular design based on a 10-slot system. The backplane configurations include:

- 10 slots + 10 slots option

- 10 slots + 6 slots + 4 slots option

- 6 slots + 4 slots + 6 slots + 4 slots option

Each cabinet within the CRAY Y-MP EL system contains a VMEbus chassis. In its maximum configuration, this VMEbus can be separated into the 6-slot, 4-slot, 6-slot, 4-slot option, resulting in a maximum of 16 IOS configurations (4 cabinets x 4 IOSs per cabinet = 16 IOSs per system). The customer decides how many IOSs to include in a system, depending on desired performance.

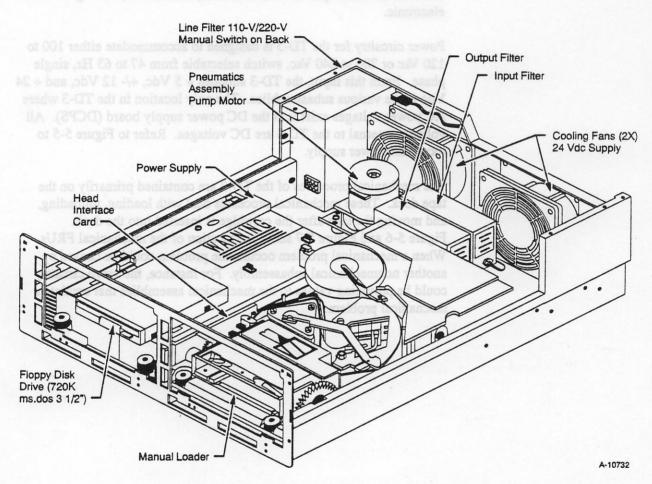

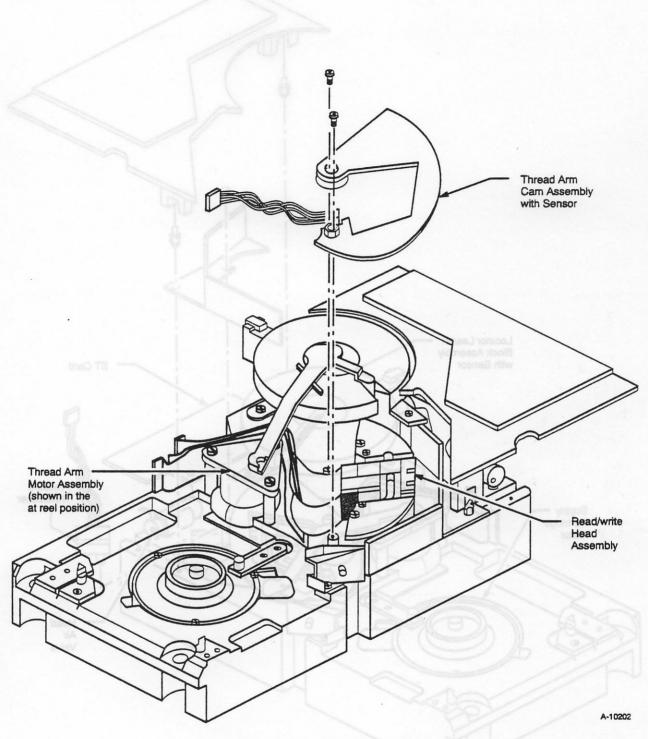

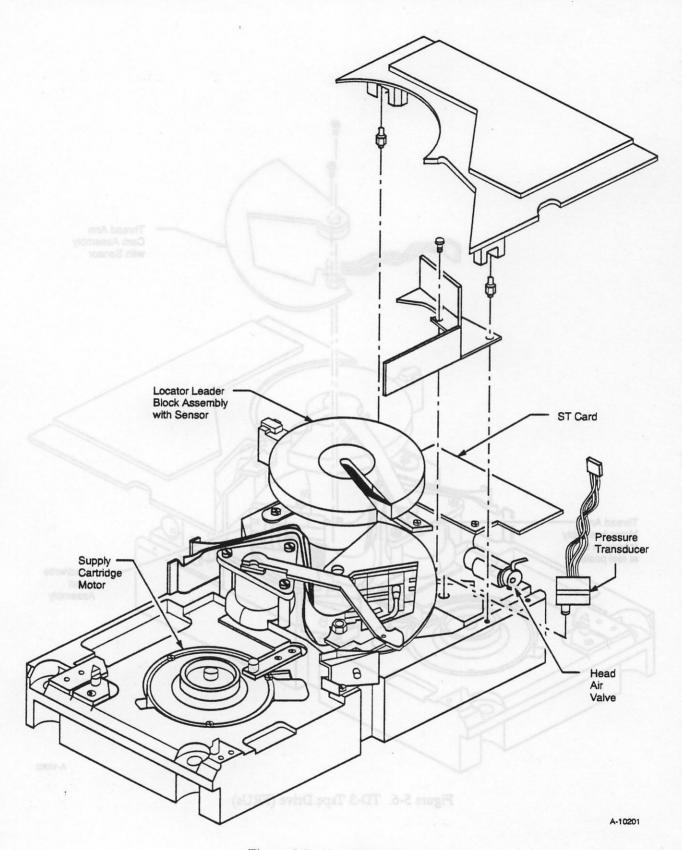

# The Maintenance SCSI

The maintenance SCSI consists of a Winchester-technology hard disk drive capable of storing 780 Mbytes of data. This disk drive maintains the IOS kernel, the diagnostic binary files, and the UNICOS operating system. Accompanying the hard drive are two separate tape drives: the EXABYTE 8-mm helical scan high-density tape drive and the standard QIC 150 streaming cartridge (0.25-in tape) tape drive.

The primary purpose of the SCSI devices is to provide a boot storage address to bring the system from a cold or dead machine state to an operating state. The maintenance SCSI also uses the tape drives to make system backup tapes or to load new operating system releases.

Because the operating system (UNICOS) resides on the maintenance hard drive, the hard drive also contains the online diagnostic functions, which are a part of UNICOS. Similarly, the offline IOS diagnostics, which are a part of the IOS kernel, are resident on the hard disk. No other maintenance diagnostics are on the hard disk.

The CRAY Y-MP EL system uses a WYSE 60 terminal as the system console. Using this system console, it is possible to boot the operating system and to perform other system functions as allowed under the operating system. This system console is an integral part of the CRAY Y-MP EL system.

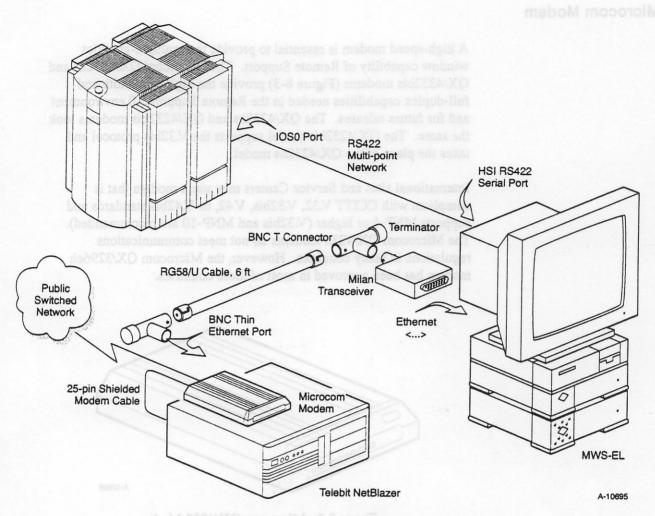

The proprietary maintenance workstation, or the MWS-EL, is connected to a separate input bus. This workstation is a Sun 4/40, and is not considered part of the CRAY Y-MP EL system. Instead, the MWS-EL is owned by the maintenance organization and is available for maintenance representative use only. This workstation provides a remote access

connection from the maintenance hub, and in the case of an on-site visit from a maintenance representative, provides a platform for maintenance functions.

The MWS-EL contains a hard disk drive with a complete copy of the mainframe maintenance environment (MME), which is used to isolate problems in the CPU or memory using the offline diagnostics available to the CRAY Y-MP EL system.

The MWS-EL is connected to the CRAY Y-MP EL system via an RS-422 connection that connects to the Heurikon V68/K30 IOS controller board in each of the incorporated IOSs. The Heurikon board, used as the IOS master processor in the IOS 0 location, acts as the MWS-EL arbitrator, and is required in that location for correct MWS-EL operation. However, all IOSs are accessible to the MWS-EL individually.

# 2 CENTRAL PROCESSING UNIT

30 nanosecond clock

of executing vector mask

(annipumani 2017)

The CRAY Y-MP EL computer system central processing unit (CPU) is a single printed circuit (PC) board module that contains all the registers and functional units normally used in a computer mainframe. This miniaturization is made possible by very large-scale integration (VLSI) complimentary metal oxide semiconductive (CMOS) application-specific integrated circuits (ASICs). Twenty-three of these ASICs are mounted on a single 16 x 22 x .093 inch PC board.

The CMOS ASICs are 1-micron, two-layer devices with 100,000 undefined gates and 299 pins, each measuring  $2.08 \times 2.08$  inches. The power consumed by these chips averages less than 5 watts per ASIC, operating at + 5 volts.

The PC board used to form the CPU module is manufactured of 16 separate layers:

- 1 top pad

- 1 bottom pad

- 4 ground (Vss) layers

- 4 power (Vdd) layers

- 6 signal layers

This module uses an average of 160 watts of power per CPU module. Therefore, the maximum of four CPU modules in a system consumes 640 watts. The CPU, like the entire CRAY Y-MP EL system, is an air cooled device.

The following nine types of ASIC chips reside on the CPU module:

- One arbiter ASIC (AR) controls memory access and arbitrates all memory conflicts. It also provides interrupting CPU synchronization.

- One address and scalar ASIC (AS) contains all of the address registers and the address functional units (FUs), as well as the scalar (S) registers and scalar FUs.

- Two channel control ASICs (CC) control or support the functions of two Y1 channels. Each of the Y1 channels is capable of 40-Mbyte/s transfers and each connects to a VME subsystem. It is also possible to use two Y1 channels in conjunction to provide one high-performance parallel interface (HIPPI) channel for 100-Mbyte/s transfers). The CC chip also contains the console bus interface, which provides console support. This function is only implemented on CC0.

- Eight data switch ASICs (DS) steer data between memory, the selected channel, and the required FUs. The DSs also contain the vector registers and some selected exchange registers.

- Four execution unit ASICs (EU) contain all of the vector and floating-point FUs, with the exception of the floating-point reciprocal FU. This format provides full pipelining to the EU chips and allows each to work on a different problem independently of the others.

The EU pipeline varies from a standard pipeline. When the EU is used as a series pipeline, the results of the computational operation must be returned to the DS ASIC, where the result data is steered before it can be used as an operand in a continuing computation.

When the EUs are used in parallel pipelines, it is possible to use all four simultaneously. In this instance, the results of the individual computations can be used in a chaining operation as continuation operands. The restrictions that pertain to the EU chips are:

- Only one FU in each EU chip can be operating at any one time

- Only the EU3 ASIC is capable of executing vector mask (VM) instructions (146 and 147, 175 instructions)

- One memory control ASIC (MC) provides address generation, which can support up to 512 Mwords of memory. The MC chip also provides both operand and program range error detection.

- Four memory data ASICs (MD) perform single-error correction, double-error detection (SECDED) functions, including check bit generation on the read and write memory data. The MDs are also used to support all of the memory maintenance instructions.

- One processor control ASIC (PC) contains the CPU instruction buffers. The CRAY Y-MP EL system CPU uses eight instruction buffers, each of which is 32 words wide. Instruction issue control and I/O interrupt handling control also reside on the PC chip. Part of the issue control function is a resource scoreboard, which also resides on the PC. Shared register access control is also performed on the PC ASIC (the CRAY Y-MP EL system supports seven shared register clusters).

- One reciprocal and control ASIC (RC) contains the floating-point reciprocal FU, the scan and clock control, and the control registers.

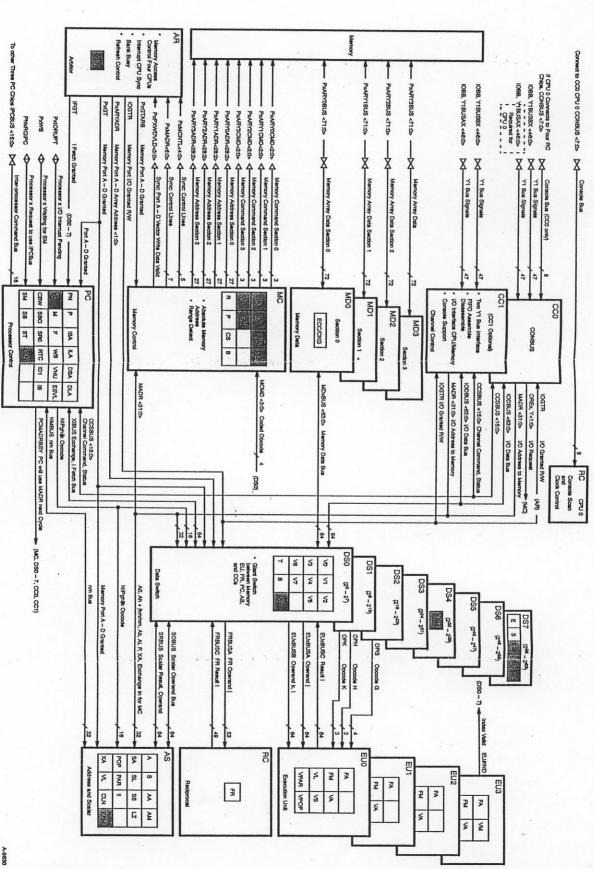

These units interconnect in the way shown on the CRAY Y-MP EL system block diagram, Figure 2-1. The signal paths are shown in more detail in Figure 2-2, a block diagram of the CPU bus. This diagram also shows the internal contents of each of the ASICs located on the CPU module. Figure 2-3 shows the actual location of the various ASICs on the CPU module.

The CRAY Y-MP EL system supports one to four CPUs. Each of these CPUs can support up to four VME subsystems. The CPU module is completely self contained and plugs into the mainframe backplane using 11 connectors that provide 1230 signal pins.

When a CPU is indicated as the faulty unit in an incident, the only onsite repair performed is the replacement of the CPU module.

The CPU module connects to the mainframe memory via four 72-bit bidirectional ports. Each of these ports connects to a separate memory section. Each of the CPU modules in a CRAY Y-MP EL system contains a copy of all memory and shared register reservations, to reduce the possibility of conflicts. Each CPU has to check its local request registers, not the request registers of all of the CPUs.

Support for multiple CPUs in the mainframe includes:

- Shared memory

- Shared registers

- Shared I/O channels

- Deadlock detection

- Shared deadstart paths

However, the CRAY Y-MP EL system does not currently support:

- Performance monitors

- High-speed (HISP) channels

- Very high-speed (VHISP) channels

Some instructions are discussed in this section, with several specific examples. Refer to Appendix A for a list of the instructions that are valid for the CRAY Y-MP EL system.

registers, not the request registers of all of the CPUs.

Figure 2-1. CRAY Y-MP EL Block Diagram

# Blank Page

Figure 2-2. CPU Bus Block Diagram

Cray Research Proprietary

# Blank Page

Figure 2-3. CPU Module

# **CPU Control**

To run a program within the CRAY Y-MP EL system, you must load the program into the selected CPU and then execute the program functions. This process includes using an exchange sequence, a fetch sequence, and an issue sequence. The exchange sequence brings the program parameters into the appropriate registers within the selected CPU. A fetch sequence immediately follows the exchange sequence and transfers a block of instructions from memory into the CPU's instruction buffers. After the instructions are loaded into the instruction buffers, the issue sequence begins moving the instructions one at a time into execution.

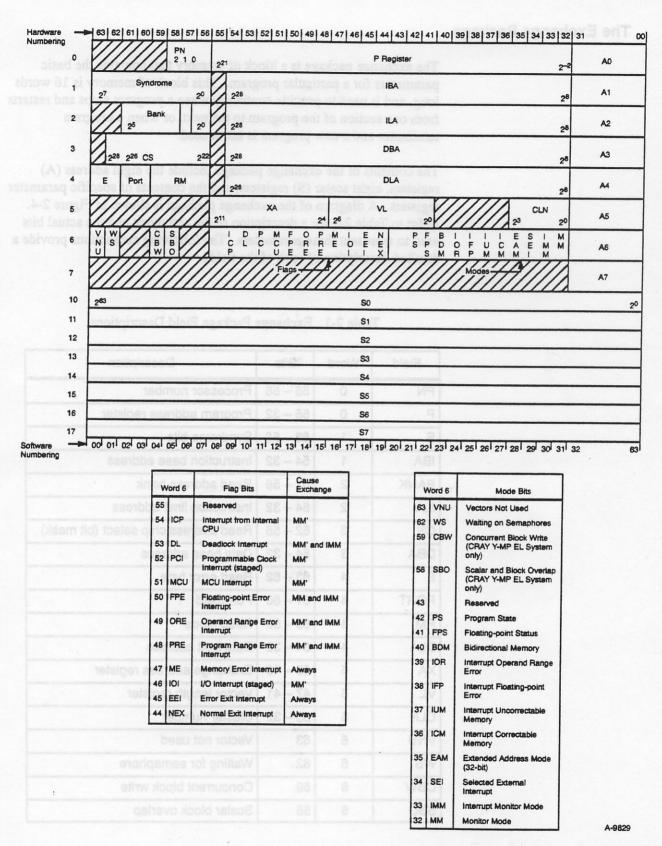

The representative diagram of the exchange package used in the CRAY Y-MP EL system, Figure 2-4, is useful for troubleshooting. The exchange package may contain pertinent information about the state of the CPU at the point of failure. To extract this information, compare the condition of the flag bits, mode bits, and the error word bits with the respective charts shown under the exchange package in Figure 2-4. In some cases, useful information can also be found in the A registers or the S registers, also shown in Figure 2-4. The usefulness of the A or S register information depends on the individual diagnostic used.

The instruction to be executed is indicated by a program address (P) register. This P register points to the location in the instruction buffer containing the desired instruction and causes that instruction to be moved into decode and then into execution. When the selected instruction is moved into the execution process, the P register increments, causing a new instruction to begin the decode process. This function continues until a desired instruction cannot be found in the instruction buffers. When this occurs, another fetch sequence is initiated, causing another block of instructions to be loaded into the instruction buffers. This process continues until the program terminates, at which time another exchange sequence occurs, allowing a new program to use the CPU.

# The Exchange Mechanism

Each CPU uses an exchange mechanism for introducing a program into execution, or for switching from one program to another. This exchange mechanism depends on a block of program parameters called an exchange package to contain the required addresses and limits imposed on the program. Another component of the exchange mechanism is the exchange sequence, which is a basic CPU operation used to load the exchange package.

Figure 2-4. Exchange Package

# The Exchange Package

The exchange package is a block of memory that contains the basic parameters for a particular program. This block of memory is 16 words long, and is used to provide continuity when a program stops and restarts from one section of the program to the next, or when a program terminates and a new program is introduced.

The contents of the exchange package include the eight address (A) registers, eight scalar (S) registers, and the contents of specific parameter registers. A diagram of the exchange package is shown in Figure 2-4. Refer to Table 2-1 for a description of the acronyms and the actual bits used to represent these parameters. The following subsections provide a detailed description of each of the fields.

Table 2-1. Exchange Package Field Descriptions

| Field | Word           | Bits    | Description                         |  |  |  |  |

|-------|----------------|---------|-------------------------------------|--|--|--|--|

| PN    | 0              | 58 – 56 | Processor number                    |  |  |  |  |

| Р     | 0              | 55 – 32 | Program address register            |  |  |  |  |

| S     | No. les les la | 63 – 56 | Syndrome bits                       |  |  |  |  |

| IBA   | 1              | 54 – 32 | Instruction base address            |  |  |  |  |

| BANK  | 2              | 61 - 56 | Read address bank                   |  |  |  |  |

| ILA   | 2              | 54 – 32 | Instruction limit address           |  |  |  |  |

| CS    | 3              | 62 – 56 | Read address chip select (bit mask) |  |  |  |  |

| DBA   | 3              | 54 – 32 | Data base address                   |  |  |  |  |

| E     | 4              | 63 - 62 | Read error type                     |  |  |  |  |

| PORT  | 4              | 61 - 60 | Port used                           |  |  |  |  |

| RM    | 4              | 59 – 56 | Read mode                           |  |  |  |  |

| DLA   | 4              | 54 – 32 | Data limit address                  |  |  |  |  |

| XA    | 5              | 55 – 48 | Exchange address register           |  |  |  |  |

| VL    | 5              | 47 – 41 | Vector length register              |  |  |  |  |

| CLN   | 5              | 35 – 32 | Cluster number                      |  |  |  |  |

| VNU   | 6              | 63      | Vector not used                     |  |  |  |  |

| ws    | 6              | 62      | Waiting for semaphore               |  |  |  |  |

| CBW   | 6              | 59      | Concurrent block write              |  |  |  |  |

| SBO   | 6              | 58      | Scalar block overlap                |  |  |  |  |

Table 2-1. Exchange Package Field Descriptions (continued)

| Field | Word  | Bits    | Description       |   |

|-------|-------|---------|-------------------|---|

| FLAGS | 6     | 55 – 44 | Flag register     | - |

| MODES | 6     | 43 – 32 | Mode register     |   |

| Α     | 0-7   | 31 – 0  | Address registers |   |

| S     | 10-17 | 63 – 0  | Scalar registers  |   |

#### **Processor Number Field**

The processor number (PN) field indicates which CPU performed the exchange sequence. The value in the PN field is inserted into the exchange package from the backplane. Logical slot 0 contains CPU 0 in the mainframe, logical slot 1 contains CPU 1, etc. Refer to Figure 3-3 for CPU slot configuration.

# **Program Address Register Field**

The program address (P) register contents are stored in the P field of the exchange package. The instruction located at this memory address is the first instruction issued when the program enters the execution phase.

#### Syndrome Field

The 8-bit syndrome field specifies the syndrome code generated from the SECDED circuits if an error occurs on a memory read operation.

### Read Address Bank Field

editte tottelv

If an error is detected during a memory read operation, the bank number of the error is retained in the 6-bit read address bank field.

# Read Address Chip Select Field

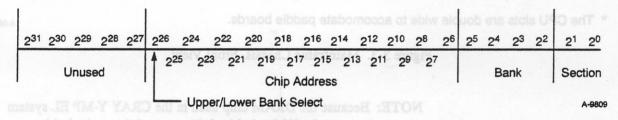

The read address chip select (CS) field identifies the chip in which a memory read error occurs. The CS bit is bit 2<sup>26</sup> of the memory read address when 1M x 4 DRAM memory chips are used.

### Read Error Type Field

The 2-bit read error (E) type field is used to determine the type of memory or I/O error detected. Bit  $2^{63}$  is set if the error is uncorrectable, and bit  $2^{62}$  is set if the error is correctable.

#### Port Field

The 4-bit port field defines the port where a memory read error or an I/O error occurs. These bits are used with the read mode bits to identify which operation was in progress when the error took place. Refer to Table 2-2 for a translation of these bits.

Table 2-2. Port and Read Mode Field Translation

| tel        | P Port Mariana 1 10   |        |                       |             |                          |        | 130 | le li       | RM Read Mode |                     |          | Port Usage            |

|------------|-----------------------|--------|-----------------------|-------------|--------------------------|--------|-----|-------------|--------------|---------------------|----------|-----------------------|

| 6          | 6                     | 6      | 6                     | 6           | 6<br>0                   | 6      | 6   | 5<br>9      | 5<br>8       | 5<br>7              | 5        |                       |

| A<br>0     | 0                     | B<br>0 | 1                     | C<br>1      | 0                        | D<br>1 | 1   | 0           | 0            | 0                   | ale<br>1 | Exchange              |

| 0          | 0                     | 0      | 2 511                 | 11:         | 0                        | H.II   | -   | 0           | 0            | nerg triq s         | 0        | A or S                |

| mon<br>upa | 19 <u>(0)</u><br>13 3 | 110    | r is <u>i</u><br>nten | 100         | 108 <u>1</u> 18<br>11801 | D<br>x | x   | 0           | onssi uoj    | 0                   | 1        | I/O single            |

| -          | -                     | -      | -                     | -           | -                        | D<br>x | x   | 0           | 1            | 1                   | 1        | I/O block             |

| 0          | 0                     | 0      | 1                     | 1           | 0                        | -      | -   | 1           | 0            | 0                   | 0        | B or T                |

| igo<br>go  | e <u>Lo</u><br>heer   | 10 KU  |                       | 1200<br>1 S | <u>(1</u> 00<br>(8 00    | D<br>x | X   | 113<br>13 0 | 0            | Septisyl<br>CDED of | 1        | Fetch                 |

| 0          | 0                     | 0      | / 1                   | 1           | 0                        | -      | -   | 1           | 1.           | 0                   | 0        | Vector stride         |

| 0          | 0                     | 0      | 1                     | 1           | 0                        | -      | -   | 1           | 1            | 1                   | 0        | Vector gather/scatter |

#### Read Mode Field

The read mode (RM) field bits are used with the port field bits to determine the read operation that was in progress when a read error occurred. Refer to Table 2-2 for a translation of these bits.

The fields described previously (syndrome, bank, CS, E, port, and RM) are referred to as the memory error data fields. These fields are valid only in the exchange package if one of two conditions are met. The first condition is that the interrupt on correctable memory (ICM) bit must be set in the mode register and a correctable memory error must be detected. This condition causes an exchange to occur. The second condition that

validates the memory error data fields is the interrupt on uncorrectable memory (IUM). This bit must be set in the mode register and an uncorrectable memory error must be detected, causing an exchange to take place. In these two instances, the exchange package contains valid data that can be useful in the repair of the CRAY Y-MP EL system, both at the field replaceable unit (FRU) level and at the component level. When possible, the contents of the exchange package memory error data fields should accompany a memory module when it is returned to central repair for evaluation and component replacement. This information can be in the form of a screen snap when a printer is available, or handwritten when no printer is available.

#### **Data Base Address Register Field**

The data base address (DBA) register field is used to hold the base, or first address of the user's data area. The base address is used to determine the location in memory of a program's data. Each time an instruction from the program makes a memory reference, the memory address generated by the instruction is added to the DBA to create the absolute memory address.

On the CRAY Y-MP EL system, the DBA is bit  $2^{54}$  through bit  $2^{32}$ , with bit  $2^{32}$  through bit  $2^{39}$  equal to zero. This condition causes the contents of this register to always be a multiple of  $400_8$ .

#### **Data Limit Address Register Field**

The data limit address (DLA) register field holds the highest address of the user's data area and is used to determine the highest absolute memory address a program can use for data. Each time an instruction makes a memory reference, the absolute memory address that is generated is compared to the address held in the DLA. If the absolute memory address is equal to or greater than the DLA value, an out-of-range condition occurs. If the absolute memory address is less than the DLA, the program is allowed to proceed.

If the out-of-range condition occurs during a memory read reference, the reference is allowed to issue and complete, but a zero value is transferred from memory. A memory write reference that exceeds the DLA is allowed to issue, but no memory write occurs.

#### Instruction Base Address Register Field

The instruction base address (IBA) register field holds the user's base address. This base address is used to determine where a program's instruction area is located in memory. When an instruction fetch

sequence occurs, an absolute memory address is created by adding the relative address generated by the fetch control logic (the upper 22 bits of the P register) to the contents of the IBA register.

# Instruction Limit Address Register Field

The instruction limit address (ILA) register field holds the limit address that has been defined as the user's instruction area. The ILA is used to determine the maximum absolute memory address that can be accessed during an instruction fetch sequence.

If the absolute memory address does not fall between the addresses contained in the IBA and the ILA, the CPU generates a program range error interrupt.

#### **Exchange Address Register Field**

The exchange address (XA) register field specifies the address of the first word of a 16-word exchange package. The XA register contains the upper 8 bits of a 12-bit area that is used to specify the absolute memory address. The lower 4 bits of this area are forced to zero, causing the conditional requirement for the exchange package to always start on a 16-word boundary. Likewise, the 12-bit limit restricts the exchange package to the lower 10000<sub>8</sub> words of memory.

### Vector Length Register Field

The vector length (VL) register field is 7 bits wide and is used to define the length of all vector operations. The length of a vector operation indicates the number of vector elements that are allowed to be used by a vector instruction. The value in the VL register can be changed during program execution by using the 00200k instruction. When the VL register is set to zero, the actual number of vector elements used is 1008 because the VL register is a circular countdown register.

#### Cluster Number Register Field

The cluster number (CLN) register field is used to determine which cluster of shared registers is used by the CPU executing the program. There are seven clusters of shared registers available for use. These clusters are composed of shared B (SB) registers, shared T (ST) registers, and semaphore (SM) registers. The exchange package contains a number between one and seven in the CLN register field, which determines which cluster of shared registers that CPU can access. To prevent a CPU from accessing any shared registers, a zero is inserted into the CLN field.

#### **Vector Not Used Field**

The vector not used (VNU) field reflects the condition of use of the vector instructions 077ijk and 140ijk through 170ijk. If none of these instructions are set in the previous execution interval (that time when the the exchange package was active), then the VNU bit is set. Any time one of the vector instructions is used during the execution interval, VNU is equal to zero.

#### Waiting for Semaphore Field

When the waiting on semaphore bit is set in the exchange package, it indicates that an exchange occurred when a test and set instruction (0034jk) was holding issue in the next instruction parcel (NIP) register area.

#### Concurrent Block Writes Bit

When the concurrent block writes (CBW) bit is set in the exchange package, the CRAY Y-MP EL system can have more than one write port active at one time. The CBW bit is specific to the CRAY Y-MP EL system, and is the first mainframe that allows more than one write port to memory. When used, the 002604 instruction enables and the 002504 instruction disables CBW.

#### Scalar Block Overlap Bit

The scalar block overlap (SBO) bit is another exchange package bit causing a CRAY Y-MP EL system specific function. The function of the SBO is to allow scalar memory references to intermix with memory block references. The 002606 instruction enables SBO, and the 002506 instruction disables SBO.

The remainder of the fields in the exchange package are definitions of the interrupt flags that are set in the exchange package if an exchange sequence is initiated by one of the interrupts, and the mode bits that are user selectable to define program execution. The contents of the A registers and the S registers are also shown in the exchange package.

# Exchange

The purpose of the exchange mechanism in the CRAY Y-MP EL system is to provide a means of switching program execution between different programs.

The exchange sequence provides a process in which the currently executing program is gracefully deactivated, with its current operating parameters placed in memory for later retrieval. The next step in the process retrieves the operating parameters of the new program from a specified memory location and places these parameters into the CPU operating registers. The CPU operating registers that are used to contain operating parameters are referred to as the exchange registers, and are spread across several ASICs on the CPU module.

There are a limited number of situations that can cause an exchange to occur, which are:

- Deadstart

- Normal program exit

- Error program exit

- Interrupt

The deadstart sequence starts a program after a power-off/power-on operation or if the operating system is initialized in the mainframe. When these situations occur, the contents of all control latches, words in memory, and all registers are considered invalid.

The mainframe is deadstarted through the IOS 0 maintenance channel, which connects CPU 0 to the IOBB in IOS 0. When a multiple-CPU system is initialized, the deadstart sequence can only occur in one CPU because only one CPU can exchange to memory location 0 at one time. The remaining CPUs in the system must wait for an interrupt from internal CPU (ICP) before they can exchange to memory location 0.

The sequence of events that take place during a deadstart exchange are as follows:

- 1. Using the scan path, set the following registers and flags:

- XA = 0

- MM = 0

- P = 000000

- NIP = 001000

- IBxV = 0

- NIPVLD = 0 (next instruction parcel valid)

- HLDISS = 1 (hold issue)

- All data channels ready to write memory

- 2. Write 006000 000000 000000 000000 to memory location 0.

- 3. For each CPU, the console sends a CPURUN ON (010000) command; CPUs will do IFETCH to location 0 and loop on the 006000 instruction.

- 4. Load the operating system and initial exchange package to location 0 from the IOS using any data channel.

- 5. Deadstart the first CPU (for example, CPU 0) by sending MCURUPT to that CPU.

- 6. While CPUs 1 through 3 remain in an idle state, CPU 0 exchanges to location 0.

- 7. When CPU 0 completes the initial exchange and becomes active, it reloads another exchange package at location 0 and sends an ICP interrupt to one of the idle CPUs, allowing that CPU to exchange to location 0 and become active.

- 8. The previous 2 steps are repeated until all CPUs in the system are active and able to perform.

NOTE: The CPUs can be deadstarted in any sequence.

Each exchange package resides in an area that is defined during initial system deadstart. This defined area must reside in the lower 4096 (10000<sub>8</sub>) words of memory. The exchange package at memory location 0 is the deadstart monitor's exchange package. Only this monitor has an area defined so that it can access all of memory, including other exchange package areas. This area allows the monitor to define or alter all exchange packages other than its own when it is the active exchange package. Other exchange packages provide for objective programs and other monitor tasks and are located outside of the programs' instruction and data areas.

There are also two exit instructions that can initiate an exchange sequence. They are the error exit instruction (000000) and the normal exit instruction (004000). These two instructions are provided so a program can request its own termination. The normal exit instruction allows a program to exchange back to the monitor area. The error exit instruction is used if an abnormal condition is detected by the object program. In this case, the program can exchange to an error handling program at a location specified by the XA field of the exchange package.

The final condition that can cause an exchange is the instance when an interrupt is received by the object program. When this occurs, the object program exchanges with another program at the address specified by the XA field of the exchange package.

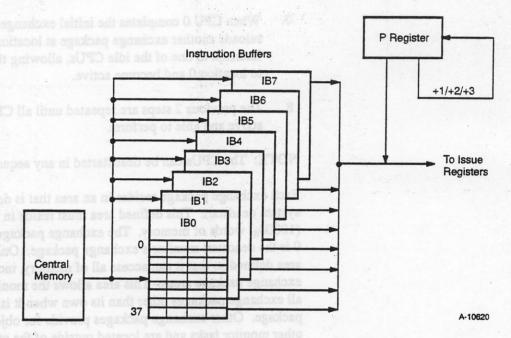

## Fetch

Any exchange sequence is immediately followed by an instruction fetch operation (a fetch), which reads program code from memory and places it in an instruction buffer. The instruction buffers hold the program code until the code is required by the execution sequence. When needed, the program code is moved from the instruction buffers into the CPU's issue registers.

The CRAY Y-MP EL system uses a P register to initiate a fetch sequence and eight instruction buffers to store the program code. Figure 2-5 shows the relationship between the P register, the instruction buffers, and central memory.

Figure 2-5. Instruction Fetch Hardware

The eight instruction buffers used by the CRAY Y-MP EL system can each hold  $40_8$  (00 through  $37_8$ ) words. Each of these  $40_8$  words is composed of four 16-bit instruction parcels, providing a total content of 128 parcels. These instruction parcels are held in the instruction buffer until they are selected by the P register to be moved into the issue registers.

The first instruction in an instruction buffer always has a word address that is a multiple of  $40_8$ . This word address allows the entire area of addresses for a single buffer to be defined by the upper 17 bits of the P register.

Each of the instruction buffers has an associated instruction buffer address register (IBAR). The IBAR contains the upper 17 bits of the P register and an IBAR valid bit. When set, the IBAR valid bit is used to indicate that the instruction buffer contains valid data. During an exchange sequence, the IBAR valid bit is cleared, which invalidates the previous program's instructions. When there are no IBAR valid bits set, an instruction fetch sequence is initiated. Note that this condition can occur during normal program execution as well as during an exchange sequence. Once the fetch sequence begins, when instructions are newly loaded into an instruction buffer, the IBAR is loaded with the upper 17 bits of the P register and the IBAR valid bit is set.

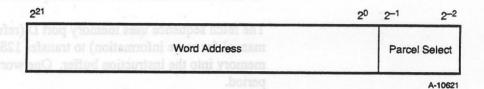

The 24-bit P register contains the address of the next parcel of program code that is to enter the NIP register. The upper 22 bits of the P register, shown in Figure 2-6, are used to indicate the word address, while the lower 2 bits are used as parcel select.

Figure 2-6. P Register

Under normal circumstances, the P register increments sequentially through the program code. This increment occurs whenever an instruction moves into the issue hardware. For a 1-parcel instruction, the P register increments by +1; a 2-parcel instruction causes a +2 increment and a 3-parcel instruction results in a +3 increment. This sequence allows all instructions to issue in 1 clock period. Branch instructions, when encountered, load the P register with the word address of the jump, allowing the program to continue. This branch can occur to another address contained in the instruction buffers, which then issues as if there were no abrupt change. However, it is also possible to issue a branch word address that is not currently held in the instruction buffers. In this instance, a fetch sequence must occur before program execution can continue.

When a program exchanges out, the P register field contains the word address of the instruction immediately following the address of the instruction that last executed.

suffer always contains the

grecuted. As an example, if

## Instruction Fetch Operation

An instruction fetch operation, or fetch, refers to the series of steps that are performed to read program code from memory into the instruction buffers.

The P register always contains the parcel address of the next instruction that is to be decoded (moved into issue). The decision to fetch is based on the comparison of the P register contents against the contents of the eight IBARs. This comparison check is done each clock period. If the contents of any one of the IBARs is equal to the upper 17 bits in the P register and the IBAR valid bit is set, a condition called in-buffer or coincidence exists and no fetch is required.

If the upper 17 bits of the P register do not match any IBAR, or the IBAR valid bit is not set, a condition called out-of-buffer or no coincidence exists. In this condition, there are no valid instructions in the instruction buffers and a fetch sequence is initiated.

The fetch sequence uses memory port D (refer to Section 3 of this manual for more information) to transfer 128 parcels ( $40_8$  words) from memory into the instruction buffer. One word is transferred each clock period.

The instruction buffers are circularly loaded. This means that a fetch sequence moves 128 parcels into the first instruction buffer, then another fetch is required to fill the next instruction buffer. This process continues sequentially until all eight instruction buffers are filled or until the ILA is reached. If a program requires more than 1024 parcels (eight fetch sequences), the ninth fetch operation overwrites the first instruction buffer used.

The first word delivered to the instruction buffer always contains the instruction that is the first instruction to be executed. As an example, if the P register contained the address 124-2 (parcel 2 of word 124), when the fetch operation started, the first word delivered to the instruction buffer will be from memory address 124.

During an instruction fetch operation, instructions are delivered to the instruction buffer at a rate of one instruction per clock period. Because of overhead, it takes 16 clock periods for the first word to arrive from memory, and an additional 2 clock periods for the first instruction to get to the NIP register. Instruction issue can occur concurrently with the fetch operation as long as the required instruction parcel is in the instruction buffer. As long as no memory conflict occurs, an instruction buffer can be loaded in 47 clock periods. However, memory conflicts can lengthen the time required to complete a fetch.

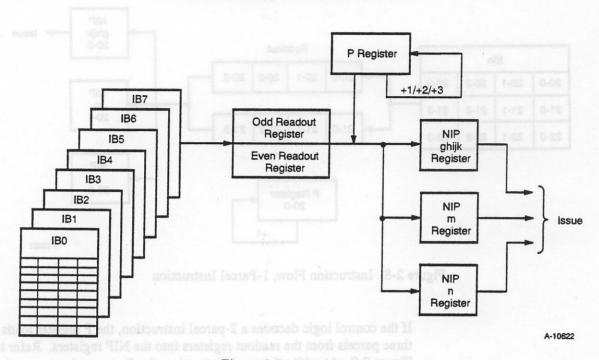

#### Instruction Issue

The CRAY Y-MP EL system makes use of three different registers as parts of the instruction issue hardware. Figure 2-7 shows the registers used, the instruction buffers, and the general flow of the instruction parcels as they move into execution.

Figure 2-7. Instruction Issue

The instruction buffers hold the program code read from memory until it is moved to the issue registers. The instruction buffers have two associated readout registers that are used to channel the flow of instructions between the instruction buffers and the next instruction parcel (NIP) registers. Even-numbered words are loaded into the even readout register, while odd-numbered words move to the odd readout register. Bit  $2^0$  of the P register determines which readout register to use, while bit  $2^{-1}$  and bit  $2^{-2}$  select the parcel that is to be sent to the NIP registers. The readout registers contain eight parcels (four even parcels and four odd parcels).

The P register value addresses the instruction buffer and moves three instruction parcels into NIPghijk, NIPm, and NIPn. These three parcels are selected from the eight available in the readout registers. At the same time the three parcels are gated into the NIP registers, the type of instruction is determined (1-, 2-, or 3-parcel) and the appropriate add (+1, +2, +3, or -1) is performed on the P register. When this add is complete, the next instruction is selected and moved into the readout registers. The cycle continues until the program terminates.

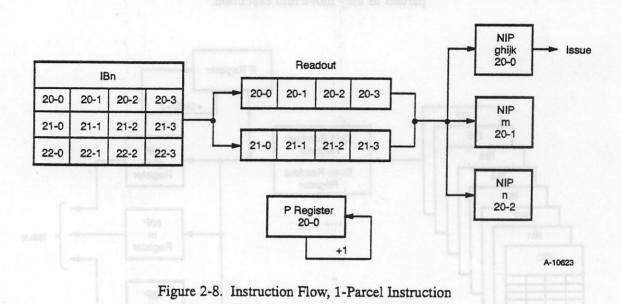

In the case of a 1-parcel instruction, the P register gates three parcels into the NIP registers. Refer to Figure 2-8. The first parcel enters register NIPghijk, the second parcel goes to register NIPm, and the third parcel enters register NIPn. If there are no conflicts, the instruction parcel located in register NIPghijk issues and the P register increments by +1.

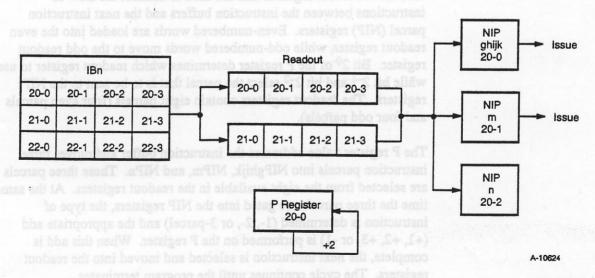

If the control logic decodes a 2-parcel instruction, the P register loads three parcels from the readout registers into the NIP registers. Refer to Figure 2-9. As with a 1-parcel instruction, the first parcel enters register NIPghijk, the second parcel enters register NIPm, and the third parcel is placed in register NIPn. If there are no conflicts, the parcels placed in register NIPghijk and register NIPm are issued, and the P register increments by +2.

Figure 2-9. Instruction Flow, 2-Parcel Instruction

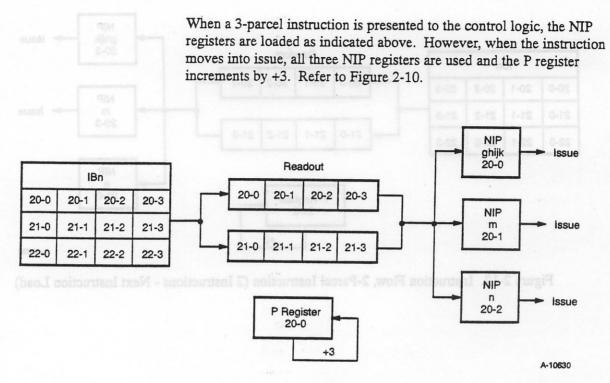

Figure 2-10. Instruction Flow, 3-Parcel Instruction

Any unused instruction parcel remaining in one of the NIP registers is

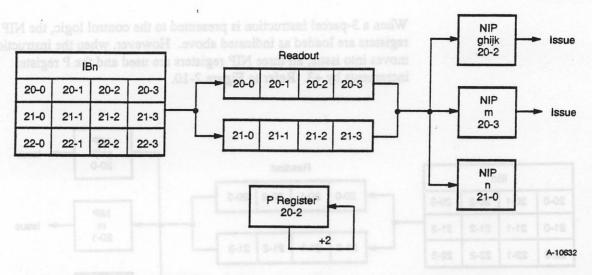

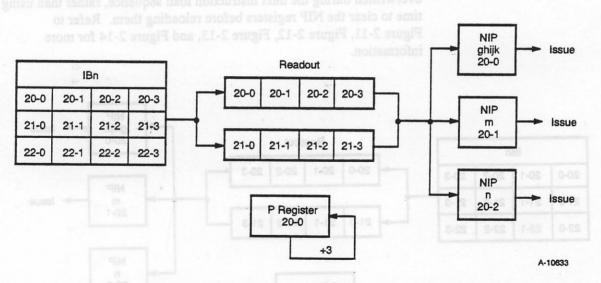

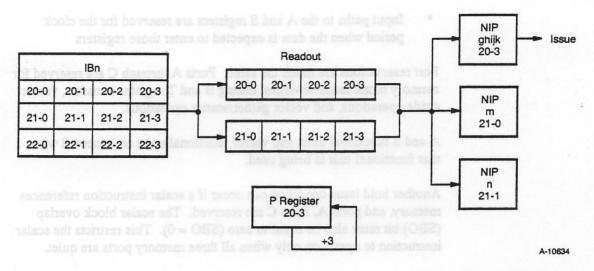

overwritten during the next instruction load sequence, rather than using time to clear the NIP registers before reloading them. Refer to Figure 2-11, Figure 2-12, Figure 2-13, and Figure 2-14 for more information. NIP ghijk Issue 20-0 Readout IBn 20-2 20-3 20-0 20-1 20-2 20-3 NIP 21-0 21-1 21-2 Issue 21-3 20-1 21-0 21-1 21-2 21-3 22-0 22-1 22-2 22-3 NIP 20-2 P Register 20-0 +2 A-10631

Figure 2-11. Instruction Flow, 2-Parcel Instruction (2 Instructions)

Figure 2-12. Instruction Flow, 2-Parcel Instruction (2 Instructions - Next Instruction Load)

Figure 2-13. Instruction Flow, 3-Parcel Instruction (2 Instructions)

Figure 2-14. Instruction Flow, 3-Parcel Instruction (2 Instructions - Next Instruction Load)

Instructions continue to flow through the issue registers until the program code exits normally or is interrupted. In either case, an exchange and fetch operation brings new code into the instruction buffers and a new value into the P register, and the issue sequence starts again. As long as there are instructions in the instruction buffers and there are no conflicts, the CRAY Y-MP EL system can issue a 1-, 2-, or 3-parcel instruction every clock period.

#### Reservations and Hold Issue Conditions

When an instruction is in the NIP registers, hardware checks are made to determine whether there are any conflicts that would prevent the instruction from completing. These conflicts are referred to as hold issue conditions, because they cause the instruction to be held in the NIP registers until the conflict condition is resolved. Once an instruction issues, reservations are immediately placed on the appropriate registers, paths, ports, or functional units required for the completion of that instruction. These reservations are held until a Reset signal is received from the appropriate resource indicating that the instruction has finished using that resource.

The conditions that cause registers to be reserved are:

- A and S registers are used as result registers

- B and T registers are used during block transfers

- V registers are reserved as either operand or result registers

the exchange package determines which cluster

Input paths to the A and S registers are reserved for the clock period when the data is expected to enter those registers

Port reservations are much the same. Ports A through C are reserved for memory block reads or writes, during B and T register transfers, vector stride operations, and vector gather/scatter operations.

A and S functional units and vector functional units are reserved when that functional unit is being used.

Another hold issue condition can occur if a scalar instruction references memory, and ports A, B, or C are reserved. The scalar block overlap (SBO) bit must also be equal to zero (SBO = 0). This restricts the scalar instruction to operation only when all three memory ports are quiet.

When using multiple parcel instructions, it is possible to have a 2-clock-period hold issue condition if the second or third parcel of the instruction is in a different instruction buffer. If the second or third parcel is not in any of the instruction buffers, a fetch operation is performed, which requires 47 clock periods to complete.

# Interprocessor Communications

Interprocessor communications on the CRAY Y-MP EL system pass data and control between CPUs. There are three elements of interprocessor communications used by the CRAY Y-MP EL system:

- Shared registers

- Semaphore registers

- Interprocessor interrupts

The purpose of the shared registers is to pass data between the CPUs. The semaphore registers synchronize the operation of a program among CPUs. The interprocessor interrupts allow one CPU to initiate an exchange sequence in a different CPU. Together, these three functions are especially useful when the CRAY Y-MP EL system is used in a multitasking environment.

The shared registers and the semaphore registers are arranged into groups, called clusters, on the CPU.

#### Clusters

The CRAY Y-MP EL system contains the shared registers and the semaphore registers into seven clusters on each CPU. A CPU may access only one cluster at a time. The cluster number (CLN) register in the exchange package determines which cluster the CPU has access to in

the specific program being run. The clusters are numbered 1 through 7. A CLN = 0 condition is used to prevent a CPU from accessing the shared registers. This function can be used to reserve a CPU in single-user mode for a specific program.

There are two ways to change the contents of the CLN register in the CRAY Y-MP EL system. One way is an exchange (refer to the Exchange subsection in this section). A second way requires the CPU to be in monitor mode and executing an 0014j3 instruction. (Refer to Appendix A for details pertaining to the CRAY Y-MP EL system instruction set.)

## **Shared Registers**

Shared registers are used to transfer data among operating registers in different CPUs. The CPU being used by a program can load its shared registers from its own operating registers. A different CPU (or several different CPUs) can then transfer this data into their shared registers, and then transfer the data from the shared registers into its operating registers. This function occurs only if the involved CPUs are all operating in the same cluster.

The CRAY Y-MP EL system contains two types of shared registers: the shared address (SB) registers and the shared scalar (ST) registers. Each cluster contains eight 32-bit SB registers, numbered SB0 through SB7, and eight 64-bit ST registers, numbered ST0 through ST7. There are four instructions associated with transferring data between the operating registers and the shared registers in a cluster of a single CPU:

| • | 026 <i>ij</i> 0 | Transmit (SBj) to Ai |

|---|-----------------|----------------------|

| • | 027 <i>ij</i> 7 | Transmit (Ai) to SBj |

| • | 072ij3          | Transmit (STj) to Si |

| • | 073ii3          | Transmit (Si) to STi |

If CLN = 0 when the CPU exchange package issues these instructions, the 026 and 072 instructions return a 0 to the designated registers, while the 027 and 073 instructions do not perform any operation.

# **Semaphore Registers**

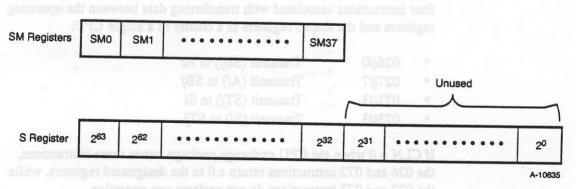

The semaphore (SM) registers enable a CPU to temporarily suspend operation of a program to allow synchronization of that CPU with other CPUs. Each cluster in a CPU contains 32<sub>10</sub> 1-bit SM registers, numbered SM0 through SM37<sub>8</sub>. During program execution, each CPU assigned to a specific operating cluster sets and clears all SM registers

within that cluster. Each of the CPUs assigned to the cluster can also transmit the contents of the SM registers to or from an S register for examination.

There are five instructions used by the SM registers:

| •    | 0034jk          | Test and set semaphore jk |

|------|-----------------|---------------------------|

| •    | 0036jk          | Clear semaphore jk        |

| 1.93 | 0037jk          | Set semaphore jk          |

|      | 072i02          | Transmit (SM) to Si       |

| •    | 073 <i>i</i> 02 | Transmit (Si) to SM       |

The 0034 instruction tests the state of the semaphore register specified in the jk field. If the content of the SMjk register is 0, the instruction executes immediately. If the content of SMjk is 1, the 0034 instruction holds issue until another CPU assigned to the same cluster clears the SMjk register. When the 0034 instruction issues in either of these cases, it sets the SMjk register to 1.

Instructions 072 and 073 are used to transfer the contents of the semaphore registers to or from the upper 32 bits of the designated S register. The relationship between the registers involved in this transfer is shown in Figure 2-15. The contents of SM0 are transferred to bit position  $2^{63}$  of the S register, while the contents of SM37 are placed in bit position  $2^{32}$ . The lower 32 bits of the selected S register are unused during this type of transfer.

Figure 2-15. Relationship between Semaphore Registers and an S Register

#### Deadlock

A deadlock is a condition that occurs when all CPUs assigned to a cluster are holding issue on an 0034jk (test and set) instruction. If this condition exists, no program execution can occur in any of the CPUs assigned to the cluster because each is waiting for one of the others to issue a clear SM (0036jk) instruction.

A deadlock interrupt resolves a deadlock condition. Then, in each of the CPUs where the interrupt occurred, the deadlock (DL) flag sets in the exchange package. This causes each of the deadlocked CPUs to execute an exchange sequence, clearing the deadlock.

Two special conditions can occur regarding a deadlock condition. First, if a CPU has a CLN = 0, a deadlock condition cannot occur because the 0034 instruction should perform no operation. If a DL flag is continuously being set, and the program is being denied execution because of this, it could be advantageous to test the 0034 instruction in an offline environment to help isolate the error.

The second condition involving a deadlock occurs only if one CPU is assigned to a specific cluster. In this case, the CPU encounters a deadlock if it issues an 0034 instruction. There is no other CPU available to clear that set condition.

#### Interprocessor Interrupts

The final segment of interprocessor communications involves interprocessor interrupts, which occur when a CPU interrupts another CPU's program. A CPU must be in monitor mode to issue the interrupt instructions. The interrupt instructions are:

• 0014j1 Set interprocessor interrupt request of CPU (Aj)

001402 Clear interprocessor interrupt request

When the 0014j1 instruction is executed, the interrupt from internal CPU (ICP) flag is set in the CPU specified by (Aj). If this CPU is not in monitor mode, it begins an exchange sequence. The program that enters the CPU is in monitor mode and issues a 001402 instruction, clearing the ICP flag. If this instruction does not execute, the CPU immediately begins another exchange sequence.

In a special case, the 0014j1 instruction is executed with the contents of Aj equal to the number of the CPU executing the instruction (the CPU is, in effect, interrupting itself), no operation is performed.

#### Real-time Clock

The CRAY Y-MP EL system has a device called the real-time clock (RTC). The RTC consists of four identical devices, one on each CPU, running synchronously to appear as one RTC to the programmer. In this discussion, the combination of circuits forming the actual RTC will be treated as a single device, since a mainframe containing only one CPU (one RTC device) performs the same as a mainframe containing four CPUs (four RTC devices).

The RTC is a 64-bit register that increments each clock period. Two instructions affect the RTC:

0014j0 Transmit (Si) to RTC

072i00 Transmit (RTC) to Si

The 0014j0 instruction can be executed by a CPU that is in monitor mode only. Two or more CPUs in monitor mode should not attempt to execute this instruction simultaneously as unpredictable results will occur. However, there is no hardware to detect this situation. The 072i00 instruction can be executed simultaneously by any number of CPUs, because only the copy of the RTC on the local CPU is read to the S register.

CPUs (four KTC devices).

# 3 MEMORY

The memory portion of the CRAY Y-MP EL computer system consists of four modules. These modules currently are provided in two types: a fully populated module and a half-populated module. Both module types are constructed on 16 x 22 x .093 inch printed circuit (PC) boards consisting of 16 circuit layers. The 16 layers are:

- 1 top pad

- 1 bottom pad

- 4 ground (Vss) layers

- 4 power layers: 5-volt application-specific integrated circuit (ASIC); 6-volt dynamic random access memory (DRAM)

- 6 signal layers

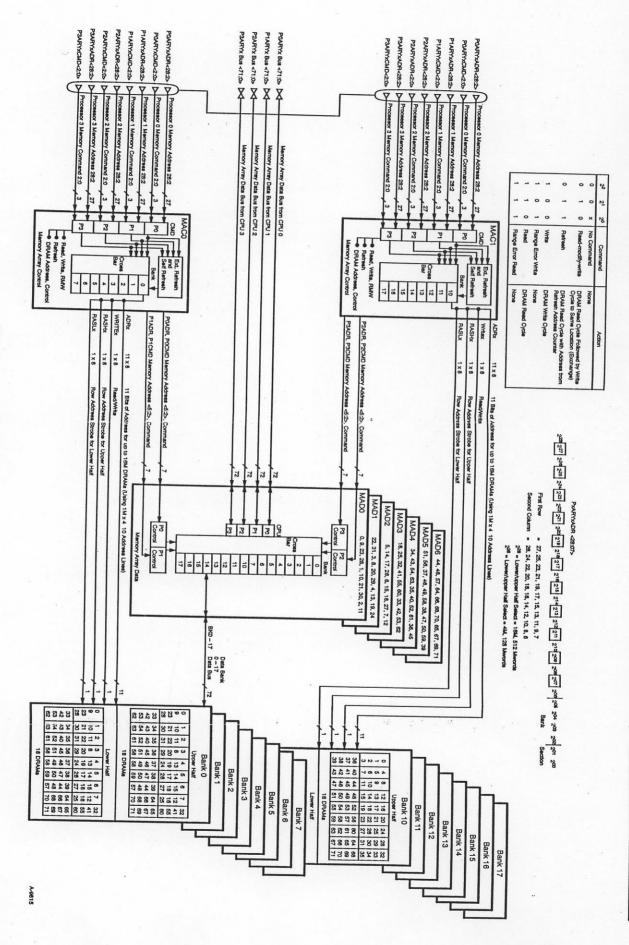

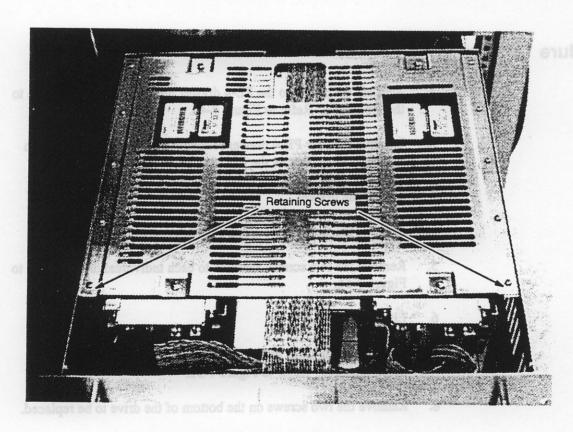

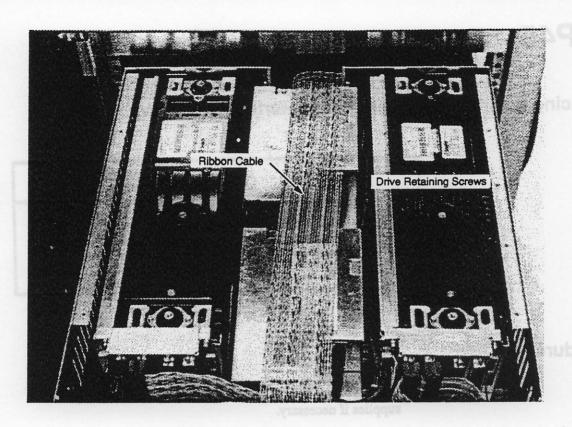

The logic portion of a memory PC board comprises two types of application specific integrated circuits (ASICs) and a group of DRAM chips. There are nine ASICs on each memory board: two memory array control (MAC) ASICs and seven memory array data (MAD) ASICs. The number of DRAM chips on each memory PC board is determined by the memory size selected by the customer. Currently, the CRAY Y-MP EL system can be supplied with either a 32-Mword memory, a 64-Mword memory, or a 128-Mword memory.

The 32-Mword and 64-Mword memory options are half-populated memory boards that contain 288 DRAM chips. Each of these DRAM chips is a 1M x 4 memory chip with a 70 nanosecond (ns) access time. The same DRAM chip is used with the 128-Mword memory, but there are 576 memory chips mounted on the fully populated memory board. Refer to Figure 3-1 for a diagram of a fully populated memory module.

Figure 3-1. Fully Populated Memory Module

Memory is divided into 16 banks for addressing whether the module is half-populated or fully populated. The fully populated module contains an upper 16 banks and a lower 16 banks of addressable memory; the half-populated module uses only the lower 16 banks. The difference between the 32-Mword and the 64-Mword memory modules is that there is one extra address bit enabled on the 64-Mword modules.

Because there are 16 banks of memory on each memory module, the mainframe has a total of 64 banks of memory. The memory is also separated into sections; each memory module is one section. This arrangement provides the mainframe with four memory sections, each consisting of 16 banks.

The CRAY Y-MP EL system uses a 32-bit address scheme, of which 27 bits (0 through 26) are used. The bits are assigned as shown in Figure 3-2. Bits  $2^0$  and  $2^1$  are used to select the appropriate section and bits  $2^2$  through  $2^5$  are used for bank selection.

Figure 3-2. Address Bit Assignments

The remainder of the address bits, with one exception, are used to select the actual memory location. The exception is bit  $2^{26}$ , which is used as the upper/lower bank select bit. This bit is only necessary on a fully populated 128-Mword memory module. The internal addressing scheme, represented by bits  $2^6$  through  $2^{25}$ , uses a row and column scheme. The odd-numbered bits are used to count the rows of memory, while the even-numbered bits are used to locate the column. To determine the failing memory module decode bits  $2^0$  and  $2^1$  to determine which section is in error. This corresponds to a specific memory module. The locations of the memory sections is shown in Figure 3-3, a representation of the eight-slot mainframe card cage. All of the memory modules are interchangeable, so swapping the suspected failing module with a good module can help isolate the failure.

<sup>\*</sup> The CPU slots are double wide to accomodate paddle boards.

A-9813

Figure 3-3. Mainframe Chassis, Front View

NOTE: Because the DRAM chip used in the CRAY Y-MP EL system memory is a 1M x 4 chip, it is expected that a single-bit error will rapidly escalate into a multiple-bit error. For this reason, it is important to repair single-bit errors as soon as possible.

Other specifications of the DRAM chip are:

- ZIP package .4 x 1.03 inch

- 5 clock period bank access time

- Standby power = 5 milliwatts at 5 volts

- Active power = 550 milliwatts at 5 volts

The rest of the memory PC board is made up of two types of MAC and MAD ASICs. The MAC ASIC chip supports four memory operations:

- Read, a normal DRAM read operation, lasts 5 clock periods.

- Write, a normal DRAM write operation, lasts 5 clock periods.

- Refresh, which uses row address strobe (RAS) to refresh data, lasts

5 clock periods.

Read/Modify/Write (RMW) is used during an exchange, and uses normal DRAM read operations followed by a normal DRAM write operation to the same address. RMW lasts 10 clock periods.

The refresh control for the DRAM chips is located on the CPU and memory PC boards.

Other functions of the MAC ASIC include:

- Connects any of the four processors to any of the 16 banks through an address crossbar

- Controls both address and control signals

- Holds a refresh address counter

- Controls all of the MAD ASICs

The MAD ASICs perform the following functions:

- Each handles a specific portion of the 72-bit memory data word

- Each contains a data crossbar which connects any of the four processors to any of the 16 banks

The interconnection between the MAD, MAC, and DRAM chips is represented in Figure 3-4. Note that MAC 0 controls operations for banks 0 through 7, and MAC 1 controls banks 10 through 17. The content of the entire data bus is presented to the seven MAD ASICs and each receives its assigned bits. The bits assigned to each MAD ASIC are in no specific order. If a random group of bits of data are reported as failing, it could in fact be a single MAD that is failing.

NOTE: When an ASIC fails, the failing chip is removed from the PC board, discarded, and replaced by a new ASIC. No internal repairs are possible. Therefore, field repair to the ASIC level is not allowed. Instead, remove and replace the memory module containing the failing ASIC.

Other important characteristics of CRAY Y-MP EL system memory modules are:

- Each memory module contains 8 Mwords or 16 Mwords of memory if half-populated and 32 Mwords if fully populated

- Operates with a 30-ns clock period

- Air cooled

Connected to the backplane by two types of connectors:

- Connected to the individual CPUs using four ports per CPU; all ports are read/write ports

- There is no hardware error logger. Single- and double-bit errors are reported to the operating system and stored in error files.

- 270 watts per module = 1080 watts per system

- Voltage = + 6 volts

NOTE: When an ASIC fails, the failing chip is removed from the PC

not allowed. Instead, remove and replace the memory module

CRAY Y-MP EL Troubleshooting and Maintenance Manual

Figure 3-4. Memory Block Diagram

# Blank Page

# **Memory Organization**

Figure 3-5 shows the major architectural features of the CRAY Y-MP EL system memory. As shown, memory is divided into four sections, each containing 16 banks. This enables simultaneous memory references (two or more memory references that begin in the same clock period) and overlapping memory references (one or more memory references that begin while another reference is in progress).

Figure 3-5. Central Memory Architecture

# **Memory Paths**

Each CPU in the CRAY Y-MP EL system has an independent path into each of the memory sections. This allows a CPU to make up to four simultaneous memory references, one to each section. Overlapping memory references are allowed to different sections without any restrictions. Likewise, overlapping memory references are allowed to the same memory section as long as each reference uses a different bank of memory. Because each CPU only has one path into each section of

memory, simultaneous memory references to the same section are not allowed, and one reference is forced to hold until the other reference completes.

Simultaneous and overlapping memory references from two or more CPUs are subject to fewer restrictions. These memory references are allowed to one section of memory. The only restriction is that each reference must use a different bank. If a simultaneous or overlapping memory reference require the same bank, a priority definition is made between the requesting CPUs. The CPU with the lowest priority is then held until the higher priority CPU has finished its reference. Refer to Table 3-1 for a summary of the proirity scheme used in the CRAY Y-MP EL system.

Table 3-1. Priority Scheme

| CPU | Section 0 | Section 1 | Section 2 | Section 3 |  |

|-----|-----------|-----------|-----------|-----------|--|

| 0   | Α         | В         | С         | D         |  |

| 1   | В         | С         | D         | Α         |  |

| 2   | С         | D         | Α         | В         |  |

| 3   | D         | Α         | В         | С         |  |

D = Lowest Priority

#### **Memory Ports**

In the CRAY Y-MP EL system, each CPU contains four memory ports for access to memory. Each of these ports has a specific function, which is defined jointly by the read mode bits and the port bits in the exchange package. Refer to Table 3-2. Ports A, B, and C are used for memory reference instructions (for details pertaining to instructions, refer to Appendix A). Port D is shared by the instruction buffers in the CPU and by the I/O section. All four ports are used for exchange operations and for refresh functions.

simultaneous memory references, one to each section. Overlapping

Table 3-2. Port and Read Mode Field Translation

| Port Bits (P) |                         |               |                      |              |      |        | Re   | Read Mode Bits (RM) |                   |                                | Port Usage   |                      |

|---------------|-------------------------|---------------|----------------------|--------------|------|--------|------|---------------------|-------------------|--------------------------------|--------------|----------------------|

| 6             | 6                       | 6             | 6                    | 6            | 6    | 6      | 6    | 5 9                 | 5<br>8            | 5<br>7                         | 5 6          |                      |

| A<br>0        | 0                       | B<br>0        | dres<br>s <b>t</b> y | C<br>1       | 0    | D<br>1 | 1 1/ | 0                   | 0                 | 10 = 0 o                       | 10011        | Exchange             |

| 0             | 0                       | 0             | 1                    | 1            | 0    | -      | -    | 0                   | 0                 | 10 page 10                     | 0            | A or S               |

| 000           | 979Ì                    | it st         |                      | 082          | to-d | D<br>x | ×    | 0                   | o ways            | 0                              | od 1         | I/O single           |

| ) as          | oillio<br>ot m          | uea<br>pa t   | i 511                | W s          | d th | D<br>x | x    | 0                   | naile<br>ios (178 | realte. 7<br>Instruct          | etet<br>beer | I/O block            |

| 0             | 0                       | 0             | 1                    | 1            | 0    | -2     | -40  | 11 lqu              | 0                 | 0                              | 0            | B or T               |

| olt;          | 0- <u>1</u> u<br>strute | 1).c<br>ni ,s | 1 = 1<br>283         | eldt<br>eldt |      | D<br>x | ×    | 1 3E                | 0                 | isa s <b>i</b> a a<br>Ban yoos | 1            | Fetch                |

| 0             | 0                       | 0             | 1                    | 1            | 0    | Comm   | 1130 | 1                   | 1                 | 0                              | 0            | Vector stride        |

| 0             | 0                       | 0             | 1                    | 1            | 0    | -      | _    | 1                   | 1                 | 1                              | 0            | Vector gather/scatte |

Port D normally has a lower priority than ports A, B, and C when it is used for I/O transfers. However, if a memory reference is forced to wait from 0 to 255 clock periods on an I/O transfer, it is given highest priority for one memory reference. When the reference begins, port D is returned to lowest priority. The actual number of clock periods used as a hold figure can be determined using the scan chain capability of the CRAY Y-MP EL system. This function is normally accomplished during the initial software tuning stage.

All of the memory ports are bidirectional. The reservation system makes use of any memory port as it becomes available, but the ports are subject to a priority system. This priority system provides a fetch sequence, with the highest priority on port D; I/O operations are given the lowest port D priority.

Ports A, B, and C operate differently when they are doing block or vector transfers than when a scalar transfer is being performed. When a port becomes available, the instruction issues and reserves the port. That port remains reserved until the instruction completes all of its memory references. After completion of the memory reference, the port reservation is cleared, and the port is available for the next instructions reservation. Under normal circumstances, a block or vector transfer is capable of reading or writing one word of data each clock period. However, if the instruction encounters a memory conflict, it is

long as they are using

suspended, or held, until the conflict is resolved. Because of this, the time needed to complete an instructions block or vector reference is unpredictable.

Block and vector transfers that use different ports are allowed to operate simultaneously, which may cause problems under certain circumstances. For example, if an 035ijk instruction precedes a 176i0k instruction that uses one or more of the same memory addresses, it is possible that some memory addresses could be read before they are written to. This is an out-of-sequence reference.

There are two ways to prevent out-of-sequence references. The first is to use the 002700 instruction, which forces completion of the memory reference. When inserted between the write instruction (035ijk) and the read instruction (176i0k), it forces the selected port to hold issue until the write instruction completes. Secondly, if the bidirectional mode (BDM) bit in the exchange package is clear (BDM = 0), out-of-sequence memory references are prevented. In this case, instructions using a port for a write operation prevent any other port from issuing a read instruction.

A scalar transfer instruction requires that ports A, B, and C be available before it can issue so that block transfers and scalar references within a CPU are sequential. A scalar reference uses one of the available ports, and consecutive scalar references are issued as long as a port is available. A scalar reference always completes in the order in which it was issued within the CPU.

The CRAY Y-MP EL system also has the added features of the concurrent block write (CBW) function and the scalar block overlap (SBO). These bits are part of the exchange package. The SBO allows scalar and block references to intermix, while CBW allows more than one block write to occur at the same time, as long as they are using different ports.

On port D, an instruction fetch sequence has priority over an I/O transfer. If a memory section conflict occurs, port D has priority over all other ports during fetch.

# **Memory Conflicts**

There are several conditions that cause memory conflicts. For example, conflicts occur when a memory port attempts to access a portion of memory that is already busy, or when two or more ports try to access the same portion of memory at the same time. Intra-CPU conflicts involve ports within the same CPU. Inter-CPU conflicts involve ports in different CPUs. In both cases, conflict resolution logic is used to impose a predetermined priority scheme to resolve the conflict.

There are three types of memory conflicts: section, simultaneous bank, and bank busy. Each of these conflicts is resolved differently.

A section conflict is caused when more than one port in the same CPU attempts to access the same memory section simultaneously. Since each CPU has only one path to each memory section, multiple references simultaneously create conflicts. These conflicts are resolved by a priority system among the four ports. The port having the highest priority is granted access to memory first. All other ports attempting a memory reference from that CPU at that time are subjected to a 1-clock-period hold issue condition. The port priority is determined using the following rules:

- Port D has priority over ports A, B, and C during a fetch sequence.