#### **CRAY-2 MEMORIES**

Clive England and David Laufer Star Wars Day 4<sup>th</sup> May 2021

#### Introduction – Sources & Placement in History

1

Hardware tour - What are we looking at ?

2

Software tour - Systems & Applications

3

Myths, Legends, Events

Questions

Especially looking to answer Questions in yellow boxes

#### Sources and references

- Senior Hardware Instructor Dan Shaw

- STCO (System Test and Check Out) on Cray-2 Paul Gage

- Engineer in charge on site SN2008 Tony Hatton

- Darkwavetech.com John Kula

- Cray history co-researcher and application software expert Alistair Mills

- Marketing and Sales literature including Cray Channels

- Cray Product familiarization training book 1987

- Cray-2 Description document Dec 1982

- HR-0200-0D CRAY-2 Computer Systems Functional Description Jun89

- The Supermen 1997, Book by Charles J. Murray

- Darkwavetech.com Cray-2 internals blog by John Kula

- The Internet

## Cray-2 place in the museum With David Laufer, Lonnie & Karin Mimms

#### Cray-2 place in early Cray Supercomputer family

```

1972

Very Approx. Time order

1996

(dates not to scale)

**T3d* --> T3e --> T3e/1200

= MPP

C1 -> XMP --> YMP --> C90 ----> T90

= PVP

= Large memory

XMS --> ELs ---> J90 -> J90se -> SV1 = Air cooled Vector supermini

APP --> SMP ---> CS6400

= Sparc Superserver

..... C3 --> C4

= Cray Computer corp.

Key:

--> Direct architectural descendant

Similar architecture but different technology

... Family ressemblance

Hosted by

Cray-2

Background CPUS slightly faster than XMP,

Four of them (a single one off 8 cpu special)

Foreground/background arrangement

Much Bigger memories

```

### Cray-2 very brief History

- Seymour Cray designed, team finished

- First Announced 1981, first delivered 1985, upgrade 1988, last one in service 1998? At NASA ???

- In media "Hunt for Red October" mention

- Place in the Cray family just along side X-MP but up to 32 times larger main memories and 4 cpus

- Cray-2 then Cray-2s and a single 8 CPU versions

- 29+1 machines built, 27 sold at typical cost \$12m .. \$17m

- And then ... Cray-3 & Cray-4 Started

#### Which one is this one?

- Some conflicting sources :

- PR came with machine has "used at NASA Langley" "has 1 billion byte memory" = 128 Mwd "Installed in 1988 used for 10 years"

- David Reports "Our Cray 2 is number 23. NASA Langley's data says they acquired it in 1988, and that it remained operational for 10 years."

- John K Reports:

- SN:2013 went to NASA Ames Research Center, Moffett Field (4 CPU/256 MW SRAM) = 2 billion bytes

- SN:2023 went to Livermore Advanced Research Center (4 CPU/127 MW SRAM )

- Cray Channels V08\_N2\_P39 has

- "Engineers working to redesign the space shuttle orbiter's main engine will be referring to numerical studies performed on the CRAY-2 computer system at NASA's Numerical Aerodynamic Simulation (NAS) facility at Moffett Field, California. ..... The most recent runs used over five million words of the CRAY-2 computer system's 256-millionword memory. The grid was generated with an elliptic generator widely used by the CFD community at the NASA Ames Research Center."

How can we tell ?

SN2023 or SN2013 ?

SRAM or DRAM ?

128Mwd or 256Mwd ?

Did NASA have more than 1?

| Background processors                 | 2    | 2    | 4    | 4    |

|---------------------------------------|------|------|------|------|

| SRAM MOS common memory (64-bit words) | 64M  | 128M | 128M | N/A  |

| DRAM MOS common memory (64-bit words) | N/A  | N/A  | N/A  | 256M |

| Disk storage units                    | 4-18 | 4-18 | 4-36 | 4-36 |

| 6- or 12-Mbyte/sec channels           | 2-8  | 2-8  | 4-16 | 4-16 |

| Magnetic tape channels                | 0-8  | 0-8  | 0-16 | 0-16 |

| 100-Mbyte/sec channels                | 0-4  | 0-4  | 0-8  | 0-8  |

#### Hardware parts - main system units

How long does it take to change a module? 20Minutes

Can areas of memory be flawed out like a bad disk drive sector?

### Hardware parts - Infographic

## What Made the Cray 2 so Revolutionary?

#### DENSELY PACKED CIRCUITS

Cray's objective was to make each new supercomputer at least ten times faster than the previous model. Microprocessors were still new, so cray opted stick with circuit boards, and to stack them into densely packed modules of 8. The Cray 2 used 320 such modules, laboriously hand wired together.

2 OPTIMIZED SYSTEM

Seymour Cray once remarked "Anyone can build a fast processor; the trick is to build a fast system. The Cray2 was both smaller and faster than its predecessors because it combined memory and processing into each module.

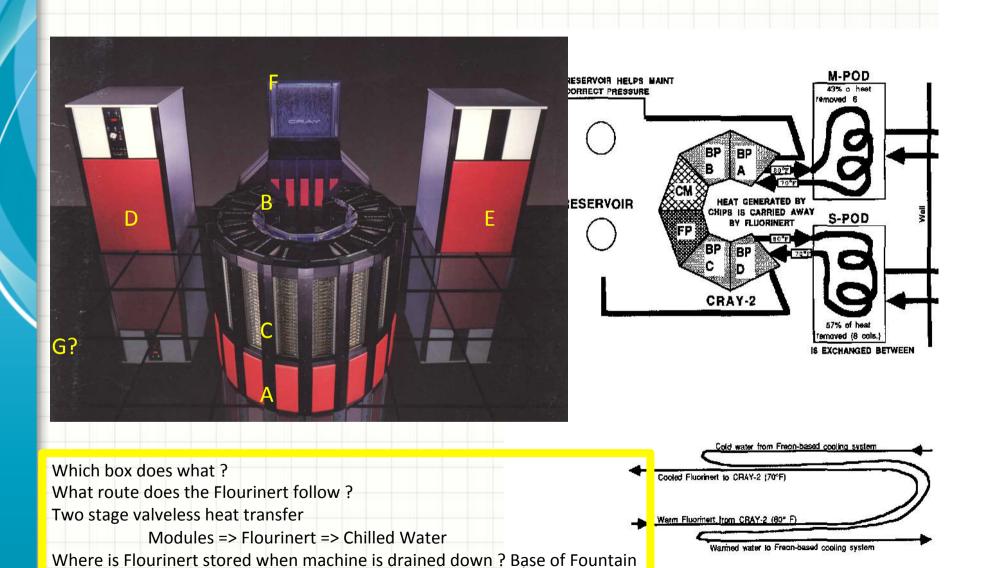

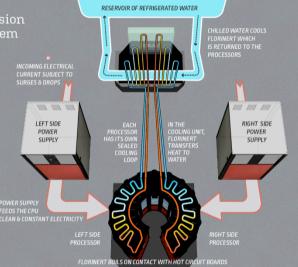

3 Liquid Emersion Cooling System

On paper, the stacked module design was very fast, but early prototypes generated way too much heatto be cooled with fans and refrigerated air. Cray's team almost abandoned the project, until they discovered Florinert, an industrial liquid that conducts heat but not electricity. This meant the Cray 2's processor and memory boards could be bathed in liquid coolant without short circuiting. This innovation made the Cray 2 faster and more reliable than

Review cooling circuit and other information To be revised....

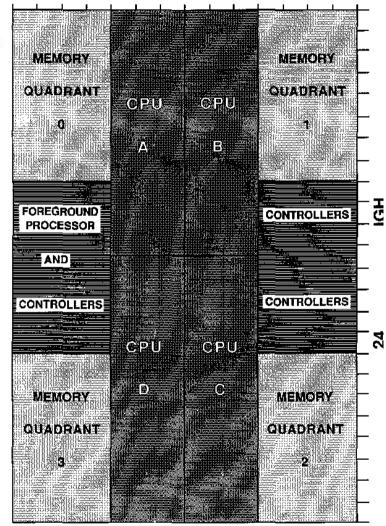

#### Hardware modules locations 4-CPU

From the above modules a variety of CRAY-2 systems can be assembled. Below is a module layout for a 4-CPU model, in this case serial number 2001.

|         |   |    | QUA | AD 0 |    | CPU A |    |    | CPU B |    |    |    | QUA |      |    |        |         |

|---------|---|----|-----|------|----|-------|----|----|-------|----|----|----|-----|------|----|--------|---------|

|         |   | A  | В   | С    | D  | E     | F  | G  | Н     | 1  | J  | K  | L   | M    | N  | N<br>D |         |

|         | A | SB | SB  | SB   | SB | FA    | AR | EA | EA    | AR | FA | SB | SB  | SB   | SB | A      |         |

|         | В | SB | SB  | SB   | SB | FB    | AM | EB | EB    | AR | FB | SB | SB  | SB   | SB | В      |         |

|         | C | SB | SB  | SB   | SB | FC    | VR | JA | JA    | VR | FC | SB | SB  | SB   | SB | C      |         |

|         | D | SB | SB  | SB   | SB | GB    | VR | JC | JC    | VR | GB | SB | SB  | SB   | SB | D      |         |

| 0       | E | SB | SB  | SB   | SB | GA    | VR | JC | JC    | VR | GA | SB | SB  | SB   | SB | E      | -       |

| n e     | F | SB | SB  | SB   | SB | VA    | VR | JB | JB    | VR | VA | SB | SB  | SB   | SB | F      | 0       |

| Channel | G | SB | SB  | SB   | SB | VB    | WA | IA | IA    | WA | VB | SB | SB  | SB   | SB | G      | Channel |

| O       | Н | SB | SB  | SB   | SB | VL    | VR | IB | IB    | VR | VL | SB | SB  | SB   | SB | Н      | Ò       |

|         | 1 |    | DA  | DA   | DA | ME    | VR | TB | TB    | VR | ME | DA | DA  |      |    | 1      |         |

|         | J |    | DB  | KA   | DB | RA    | VR | TC | TC    | VR | RA | DB | DB  |      |    | J      |         |

|         | K |    | DA  | KB   | MD | MA    | VR | TA | TA    | VR | MA | MD | DA  |      |    | K      |         |

|         | L |    | DA  | KC   | MC | MB    | QB | TD | TD    | QB | MB | MC | DA  |      |    | L      | 1       |

|         | M |    |     | DA   | MC | MB    | QB | TD | TD    | QB | MB | MC | DA  | 228  | 1  | M      |         |

|         | N |    |     | DA   | MD | MA    | VR | TA | TA    | VR | MA | MD | DA  | 77.0 |    | N      |         |

|         | 0 |    |     | DB   | DB | RA    | VR | TC | TC    | VR | RA | DB | DB  |      |    | 0      |         |

|         | P |    |     | DA   | DA | ME    | VR | TB | TB    | VR | ME | DA | DA  |      |    | P      |         |

| m       | Q | SB | SB  | SB   | SB | VL    | VR | IB | IB    | VR | VL | SB | SB  | SB   | SB | Q      | C       |

| Channel | R | SB | SB  | SB   | SB | VB    | WA | IA | IA    | WA | VB | SB | SB  | SB   | SB | R      | Channa  |

| har     | 5 | SB | SB  | SB   | SB | VA    | VR | JB | JB    | VR | VA | SB | SB  | SB   | SB | 5      | 0       |

| 0       | T | SB | SB  | SB   | SB | GA    | VR | JC | JC    | VR | GA | SB | SB  | SB   | SB | T      |         |

|         | U | SB | SB  | SB   | SB | GB    | VR | JC | JC    | VR | GB | SB | SB  | SB   | SB | U      |         |

|         | V | SB | SB  | SB   | SB | FC    | VR | JA | JA    | VR | FC | SB | SB  | SB   | SB | V      |         |

|         | W | SB | SB  | SB   | SB | FB    | AM | EB | EB    | AM | FB | SB | SB  | SB   | SB | W      |         |

|         | X | SB | SB  | SB   | SB | FA    | AR | EA | EA    | AR | FA | SB | SB  | SB   | SB | X      |         |

|         |   | A  | В   | C    | D  | E     | F  | G  | Н     | 1  | J  | K  | L   | M    | N  |        |         |

4 cpu module map Credit: Darkwavetech.com See notes for Module Key

This could be wrapped like wallpaper round the machine To show the module types/locations ( see key )

4 CPU system

24 modules high

14 columns

Product famiz doc

### Hardware modules key 4-CPU

From the above modules a variety of CRAY-2 systems can be assembled. Below is a module layout for a 4-CPU model, in this AR Address registers case serial number 2001.

|         |   |    | QUA | AD 0 |    | CPU A |       |       | CPU B |    |    |    | QUA |            |    |   |              |

|---------|---|----|-----|------|----|-------|-------|-------|-------|----|----|----|-----|------------|----|---|--------------|

|         |   | Α  | В   | С    | D  | E     | F     | G     | Н     | 1  | J  | K  | L   | M          | N  |   |              |

|         | Α | SB | SB  | SB   | SB | FA    | AR    | EA    | EA    | AR | FA | SB | SB  | SB         | SB | A |              |

|         | В | SB | SB  | SB   | SB | FB    | AM    | EB    | EB    | AR | FB | SB | SB  | SB         | SB | В |              |

|         | C | SB | SB  | SB   | SB | FC    | VR    | JA    | JA    | VR | FC | SB | SB  | SB         | SB | C |              |

|         | D | SB | SB  | SB   | SB | GB    | VR    | JC    | JC    | VR | GB | SB | SB  | SB         | SB | D |              |

| 0       | E | SB | SB  | SB   | SB | GA    | VR    | JC    | JC    | VR | GA | SB | SB  | SB         | SB | E | $\leftarrow$ |

| Channel | F | SB | SB  | SB   | SB | VA    | VR    | JB    | JB    | VR | VA | SB | SB  | SB         | SB | F | Channel      |

| har     | G | SB | SB  | SB   | SB | VB    | WA    | IA    | IA    | WA | VB | SB | SB  | SB         | SB | G | har          |

| 0       | Н | SB | SB  | SB   | SB | VL    | VR    | IB    | IB    | VR | VL | SB | SB  | SB         | SB | Н | O            |

|         | 1 |    | DA  | DA   | DA | ME    | VR    | TB    | TB    | VR | ME | DA | DA  |            |    | 1 |              |

|         | J |    | DB  | KA   | DB | RA    | VR    | TC    | TC    | VR | RA | DB | DB  |            |    | J |              |

|         | K |    | DA  | KB   | MD | MA    | VR    | TA    | TA    | VR | MA | MD | DA  |            |    | K | 8            |

|         | L |    | DA  | KC   | MC | MB    | QB    | TD    | TD    | QB | MB | MC | DA  |            |    | L |              |

|         | M |    |     | DA   | MC | MB    | QB    | TD    | TD    | QB | MB | MC | DA  | <u>=28</u> |    | M | i i          |

|         | N |    |     | DA   | MD | MA    | VR    | TA    | TA    | VR | MA | MD | DA  |            |    | N |              |

|         | 0 |    |     | DB   | DB | RA    | VR    | TC    | TC    | VR | RA | DB | DB  |            |    | 0 |              |

|         | P |    |     | DA   | DA | ME    | VR    | TB    | TB    | VR | ME | DA | DA  |            |    | P |              |

| m       | Q | SB | SB  | SB   | SB | VL    | VR    | IB    | IB    | VR | VL | SB | SB  | SB         | SB | Q | 7            |

| nue     | R | SB | SB  | SB   | SB | VB    | WA    | IA    | IA    | WA | VB | SB | SB  | SB         | SB | R | ne           |

| Channel | 5 | SB | SB  | SB   | SB | VA    | VR    | JB    | JB    | VR | VA | SB | SB  | SB         | SB | S | Channel      |

| 0       | T | SB | SB  | SB   | SB | GA    | VR    | JC    | JC    | VR | GA | SB | SB  | SB         | SB | T | 0            |

|         | U | SB | SB  | SB   | SB | GB    | VR    | JC    | JC    | VR | GB | SB | SB  | SB         | SB | U |              |

|         | V | SB | SB  | SB   | SB | FC    | VR    | JA    | JA    | VR | FC | SB | SB  | SB         | SB | V |              |

|         | W | SB | SB  | SB   | SB | FB    | AM    | EB    | EB    | AM | FB | SB | SB  | SB         | SB | W |              |

|         | X | SB | SB  | SB   | SB | FA    | AR    | EA    | EA    | AR | FA | SB | SB  | SB         | SB | X |              |

|         |   | A  | В   | C    | D  | E     | F     | G     | Н     | 1  | J  | K  | L   | M          | N  |   |              |

|         |   |    | QUA | AD3  |    | (     | CPU D | CPU D |       |    |    |    | QUA | AD 2       |    |   |              |

**4** CPU system 24 modules high 14 columns Product famiz doc

Module Key AM Address multiply

EA Foreground processor port

EB Foreground processor port

- Channel Function Decodes, Foreground Access Register

- Interrupt Address Register, Data Buffer

- Length Register. Status Register

- Common Memory Error Address . I/O Memory Reference Control

- Common Memory Address Register

DA - DD-19/DD-29 Disk Controller

DB - External I/O controller

DC - DD-39/DD-49/DD-40 Disk Controller

DD/DE - HISP/HSX Channel controller

**FA Floating Point Addition**

**FB Floating Point Addition**

FC Floating Point Addition

GA Scalar Integer Add, Scalar Population Count, and Scalar Leading Zero Count

**GB** Scalar shift

IE Instruction buffers

IF Instruction buffers

JA Main issue module

JB Main issue module (CPU issue logic that could not fit on JA)

JC Main issue module - Each JC controls 4 VR modules

(each VR is 8 bits of the Vector registers, S registers and some of the vector

and Scalar logical operations. There are 2 JC modules.)

KA Foreground CPU

**KB Foreground CPU**

KC Foreground CPU

MA Floating multiply, reciprocal, reciprocal square root

MB Floating multiply, reciprocal, reciprocal square root

MC Floating multiply, reciprocal, reciprocal square root

MD Floating multiply, reciprocal, reciprocal square root

ME Floating multiply, reciprocal, reciprocal square root

Qx\* Memory access control

RA Look up for reciprocal and reciprocal square root

Sx\* Memory module

TA Memory interface modules, packetize address and data, SECDED

TB Memory interface modules, packetize address and data, SECDED

TC Memory interface modules, packetize address and data, SECDED

TD Memory interface modules, packetize address and data, SECDED

VA Vector integer adder

VB Vector shift

VL Vector Logical, Real-time counter, vector mask register

VR Scalar Logical, Scaler Register, Vector registers, 8 modules each with 8 bits

WA Local memory:1

#### Question

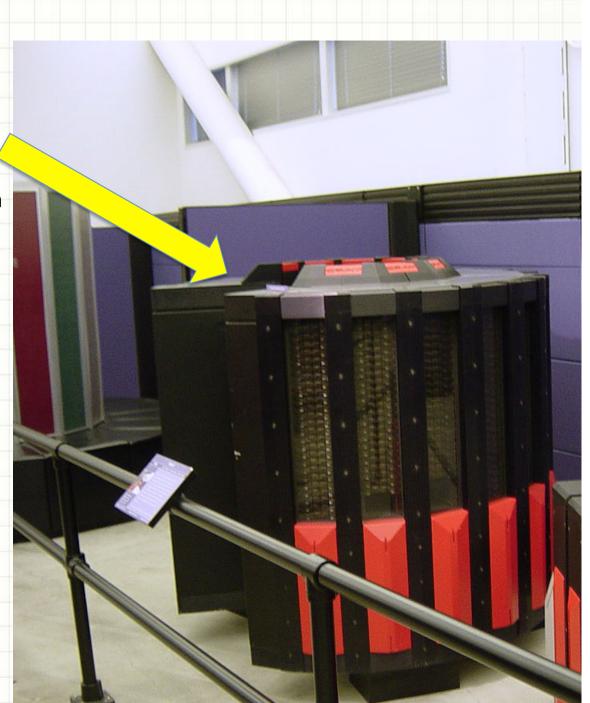

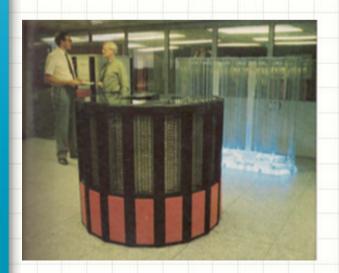

Q: What's this lump on top? Others are flat.

A: Just design feature only seen on SN2101 the 8 CPU Cray-2

A Cray-2 and its Fluorinert-cooling "waterfall", formerly serial number 2101, the only 8-processor system ever made, for NERSC

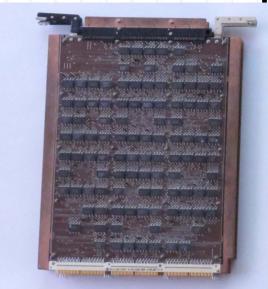

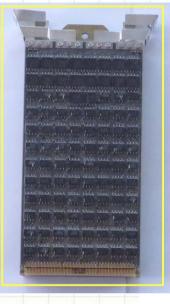

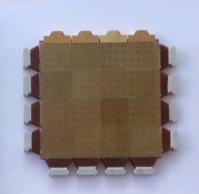

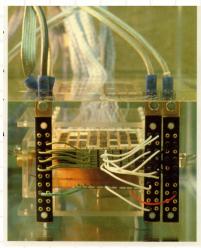

## Hardware parts – A Module

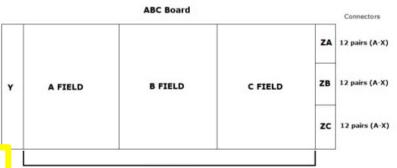

#### Fields of a Cray-2 Module Printed Circuit Board

Each board of an eight board module is divided into fields. The majority of the area of a board is allocated for three fields of gate array chips. A single letter defines each chip field. This letter corresponds to the letter that was used to define the board of the module. These chip fields contain gate array chips, termination resistors, and inter-board jumper pins. The second type of field, labeled the Y field, is located on the power bus end of each board. The Y field is used exclusively for inter-board jumper pins. The third field is located on the connector end of each board. This field is labeled the Z field. The Z field is where the connector is attached.

#### Each Module:

- 8 interconnect boards

- 8 \* 4 inches

- 6 layers

Which worked best on modules pins or holes?

Credit: Darkwavetech.com

**Chip Fields**

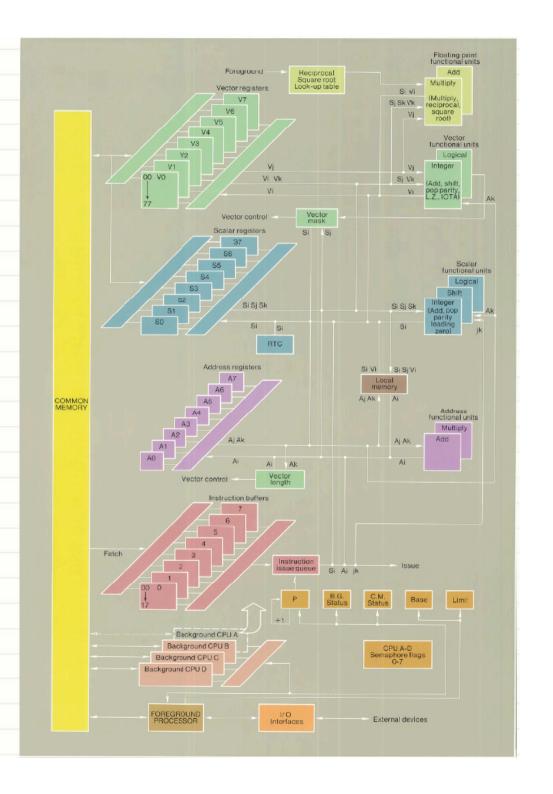

## CPU – internals block diagram

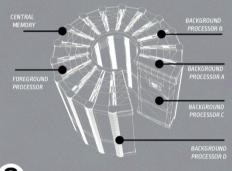

The heart of the machine was a combination of 1 controlling foreground processor that orchestrated the up to 4 workhorse background processors and all the peripheral devices.

Scalar, Vector and Address registers along with Instruction buffers hold the CPU data.

Each background processor also had 16k of local working memory and access to shared semaphore flags.

A huge central shared memory was directly accessible from any processor.

I/O all controlled by Foreground processor. (The 8p special had 2 foreground processors)

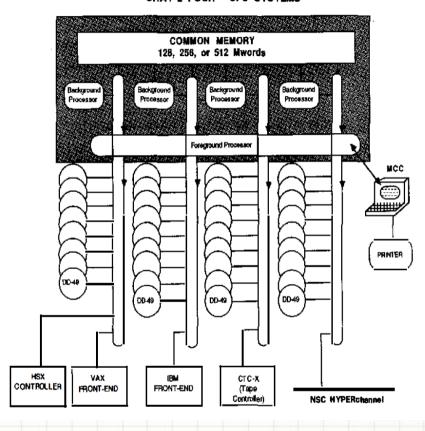

#### Hardware parts - peripherals & Network

#### Crav-2 Four CPU machine

UP TO 40 PERIPHERAL DEVICES INCLUDING: UP TO 9 DS-40 SUBSYSTEMS TOTALING 36 DD-40 DISKS STORAGE UNITS (72 WITH SHADOWING) UP TO 36 DD-49 DISK DRIVES UP TO 8 HIGH-SPEED EXTERNAL 100 Mbyte/s CHANNELS (HSX-1) CONTROLLERS UP TO 16 EXTERNAL I/O CONTROLLERS SUCH AS: FRONT-END INTERFACES (FEI) **CRAY-2 TAPE CONTROLLERS (CTC)** OR HYPERchannel ADAPTORS (A 130)

#### **Cray-2 Two CPU machine**

UP TO 20 PERIPHERAL DEVICES INCLUDING: UP TO 4 DS-40 DISK SUBSYSTEMS TOTALLING 16 DD-40 DISK STORAGE UNITS (32 WITH SHADOWING) **UP TO 18 DD-49 DISK DRIVES** UP TO 4 HIGH-SPEED EXTERNAL 100 Mbyte/s CHANNEL (HSX-1) CONTROLLERS UP TO 8 EXTERNAL 110 CONTROLLERS SUCH AS: FRONT-END INTERFACES (FEI) **CRAY-2 TAPE CONTROLLERS (CTC)** OR HYPERchannel ADAPTORS (A130)

#### CRAY-2 FOUR - CPU SYSTEMS

Any strange device hookups? Mostly just comms devices

## Software tour - System

Unicos – 1.0 - First Cray System to use Unix.

No need for Station software or managed front end as Unicos has TCP/IP. Batch job entry via frontends still used.

#### Language compilers

CFT2 based on Cray Fortran CFT

CFT77 ANSI Leading edge in compiler development

Pascal and Cray C

Assembler language

Micro and Macro tasking

#### NQS, Interactive Shells

Maintenance Control Console MCC

Thought to be a Compac or similar Pc

What did this do?

Run diagnostics, bootstrap the machine, load

software, login to machine,

## Software tour – Applications & notable customers

Kings Cross Underground station disaster – Understanding How Fire spreads Analysis From CC Astronomy, CAD visualizations, Lots of CFD eg. Hull and Wing design, Helicopter and Turbine blade design

SN2010 went to NTT (4 CPU/256 MW SRAM) – Japan Telecoms

SN2011 went to AFSCC (4 CPU/128 MW SRAM) – US Air Force Kirkland

SN2013 went to NASA Ames Research Center, Moffett Field (4 CPU/256 MW SRAM)

SN2015 went to Falcon AFB (NBT) (4 CPU/127 MW SRAM) – US Air Force Falcon

SN2023 went to Livermore Advanced Research Center (4 CPU/127 MW SRAM)

SN2027 went to CNRM (Centre National de Recherches Meteorologiques) Toulouse (4 CPU/256 MW SRAM)

Who got the 8 CPU version? NERSC

What other Applications and Sites used Cray-2?

What problems were solved and what new scientific ground was broken using this and other Cray hardware?

## Cray Channels stories

Link cc\_v03\_n2\_OCRNew.pdf# page=14

V03\_N2 1981 ?

Cray announces breakthrough in computer development Cray-2 Prototype photo Also Org chnages of Cray stepping back.

Link

cc\_v07\_n2\_OCRNew.pdf# page=4

V07\_N2 Summer 85

Introducing the Cray-2

Architecture and design overview.

Link

cc\_v08\_n1\_OCRNew.pdf# page=35

V08\_N1

CRAY-2 computer renders architecture in 3-D

Computer-generated images such as these views of the Minnesota state capitol can be valuable design and marketing tools for architects and developers

Link

cc\_v08\_n2\_OCRNew.pdf# page=41

V08\_N2

**NASA-Ames**

CRAY-2 computer system takes a slice out of pi CRAY-2 computer system aids shuttle engine design

Link

cc\_v10\_n2\_OCRNew.pdf# page=42

V10\_N2

CRAY-2 system performs star search

The sky is no limit for a team of as astronomers at the University of Minnesota. By linking the university's CRAY-2 computer system and a high-speed measuring machine used to scan photographic plates, they are analyzing the sky statistically

Link

cc\_v10\_n4\_OCRNew.pdf# page=6

Larger memory and better performance make the new **CRAY-2/4-512** computer system an exciting addition to the CRAY-2 series of computer systems.

Alistair and Clive working on building a Cray Channels web index reference system

## Myths, Legends and factoids

- Cooling First reservoir design was tubes later a rectangle reservoir was used because of crazing problems with the Acrylic tubes

- Cray-2 was first Cray system to use Unix derived operating system Unicos.

- Unicos allowed direct interactive access to machine from remotely connected users using tcp/ip ( did not need a front end station) ARPANET

- Wire lengths 5.6 miles of blue and white twisted pairs.

- Cooling liquid flows at 1 inch a second across modules

- Four background processors running with a clock period of 4.1

nanoseconds offer an effective throughput six to twelve times that of the

original CRAY-1.

- A single 8 CPU system SN2101 was built for NERSC

- Technicians could test individual modules in a flourinert bath test fixture.

The probes had marks like a ruler so they could tell how far into the module they were probing.

- There were two "Quads". They were ¼ of a full chassis. One was used for software development in the twin cities, the other was used in STCO for module screening (and doing my homework for a programming class).

What can you add here?

## Four best features of the Cray-2

- Density of electronics, it's a very small machine compared to contemporaries.

- Speed of processor using a 4 nano second clock way ahead of it time

- Size of main memory up to 30 times size of Cray-1 & XMP could run problems that would bog down on other systems. Very good at CFD codes.

- First Cray with direct interactive access for users along side batch work. Due to using Unix as base for Unicos operating system

#### Darkwavetech.com

You may be interested in the information about a Cray-2 logic emulation project and recreation along with a detailed description of Cray-2 modules and systems

By John Kula

https://www.darkwavetech.com/index.php/cray2blog/

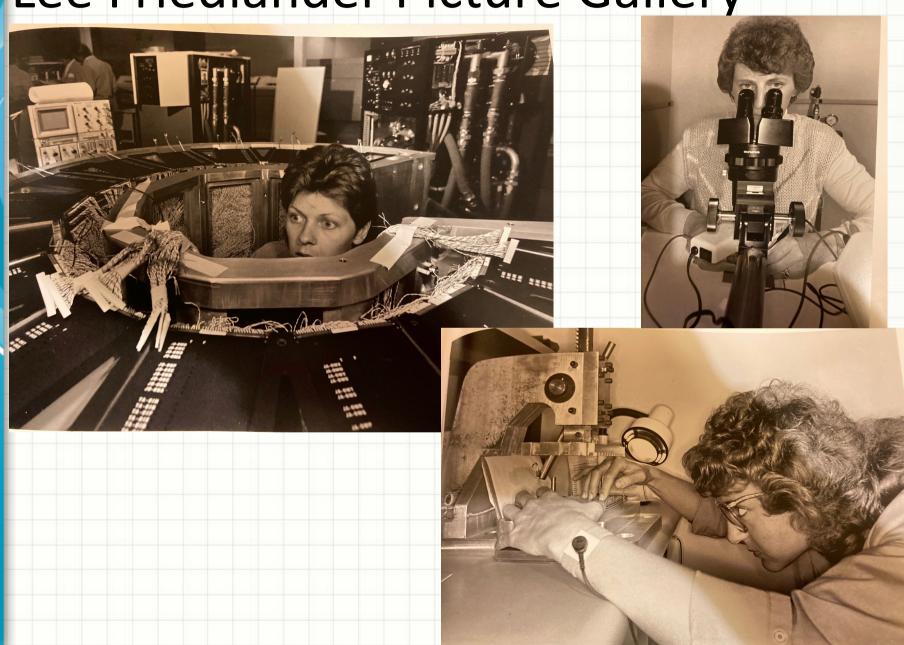

# Final Picture Gallery

## Lee Friedlander Picture Gallery

#### Wrap-up

- Thank you for your time and contributions.

- Presentation will be updated with your contributions and re-shared/reused.

- Let us know if you are interested in similar occasional meetings based around other Cray systems in the museum.

- Follow-up to

- Clive@spikynorman.net

- davidl@brandbook.us