# THE CRAY-1 COMPUTER

PRELIMINARY

CAL ASSEMBLER

**REFERENCE MANUAL**

COPYRIGHT (C) 1975 BY CRAY RESEARCH, INC. THIS MANUAL, OR PARTS THEREOF, MAY NOT BE REPRODUCED IN ANY FORM WITHOUT PERMISSION OF CRAY RESEARCH, INC. THIS MANUAL CONTAINS PRELIMINARY INFORMATION WHICH IS SUBJECT TO CORRECTION AND CHANGE WITHOUT FORMAL NOTICE TO COPY HOLDERS. New features, as well as changes, deletions, and additions to information in this manual are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

|          | REVISION RECORD                                               |  |  |  |  |  |  |

|----------|---------------------------------------------------------------|--|--|--|--|--|--|

| REVISION | DESCRIPTION                                                   |  |  |  |  |  |  |

| 4/75     | Original Printing                                             |  |  |  |  |  |  |

| A        | This revision corrects various typographical and technical    |  |  |  |  |  |  |

| 6/75     | errors.                                                       |  |  |  |  |  |  |

| В        | This revision corrects various typographical and technical    |  |  |  |  |  |  |

| 12/75    | errors, Changes have been made to the block transfer instruc- |  |  |  |  |  |  |

|          | tions. The title of this manual has been changed to the       |  |  |  |  |  |  |

|          | Preliminary CAL Assembler Reference Manual.                   |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          | -                                                             |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          |                                                               |  |  |  |  |  |  |

|          | 1                                                             |  |  |  |  |  |  |

Publication Number 2240000

# CONTENTS

| Introduction                                 |

|----------------------------------------------|

| Summary of machine characteristics           |

| Principal operating registers                |

| A registers                                  |

| B registers                                  |

| S registers                                  |

| T registers                                  |

| V registers                                  |

| VL register                                  |

| VM register                                  |

| P register                                   |

|                                              |

| Supporting registers                         |

| BA register                                  |

| LA register                                  |

| XA register                                  |

| Fregister                                    |

| M register                                   |

| Input/Output                                 |

|                                              |

| Comparison of scalar and vector processing 6 |

| Functional units                             |

| Instruction formats                          |

| Special register values                      |

| Instruction buffers                          |

| Data formats                                 |

iii

| CAL language structure   |

|--------------------------|

| Statement format         |

| Location field           |

| Result field             |

| Operand field            |

| Comments field           |

| Coding conventions       |

| Comments statement       |

| Lower case in comments   |

| Symbols                  |

| Special element, *       |

| "P." prefix              |

| "W." prefix              |

| Expressions              |

| CPU register designation |

| Pseudo-instructions      |

| ABS                      |

| BSS                      |

| BSSZ                     |

| CON                      |

| EJECT                    |

| END                      |

| ENTRY                    |

| =                        |

| IDENT                    |

| LIST                     |

| ORG                      |

| CPU instructions         |

| Appendix A. | Summary of CPU instructions 60 |

|-------------|--------------------------------|

| Appendix B. | Instruction timing ,           |

| Appendix C. | Coding examples                |

| Appendix D. | Use of the NOVA CAL assembler  |

| Appendix E. | Assembly errors                |

| Appendix F. | Description of binary output   |

v

# FIGURES

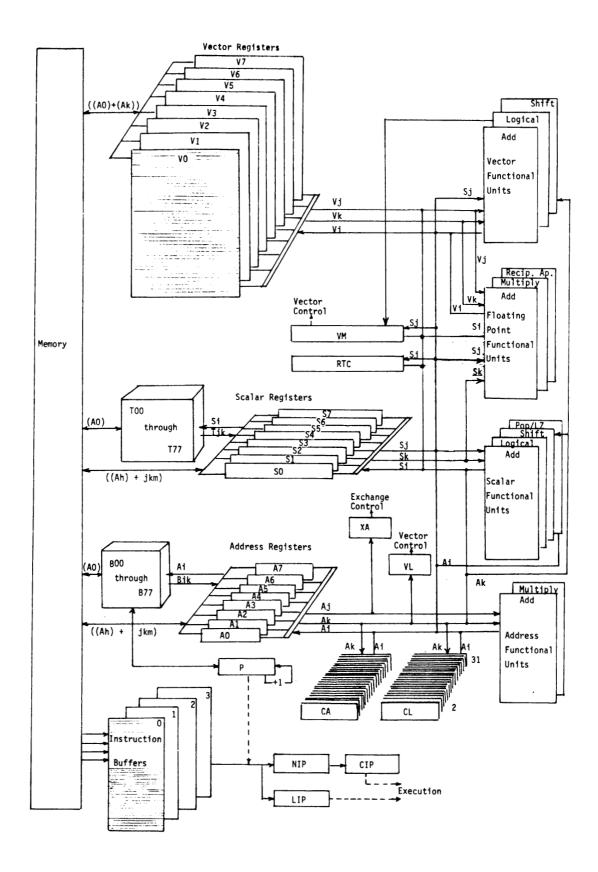

| Figure | 1. | Registers block diagram . | • | • | • • | • | • | • | • | • | • | • | • | • | • | • | 3  |

|--------|----|---------------------------|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|----|

| Figure | 2. | Exchange package          | • | • | • • | • | ٠ | • | • | • | • | • | • | • | • | • | 4  |

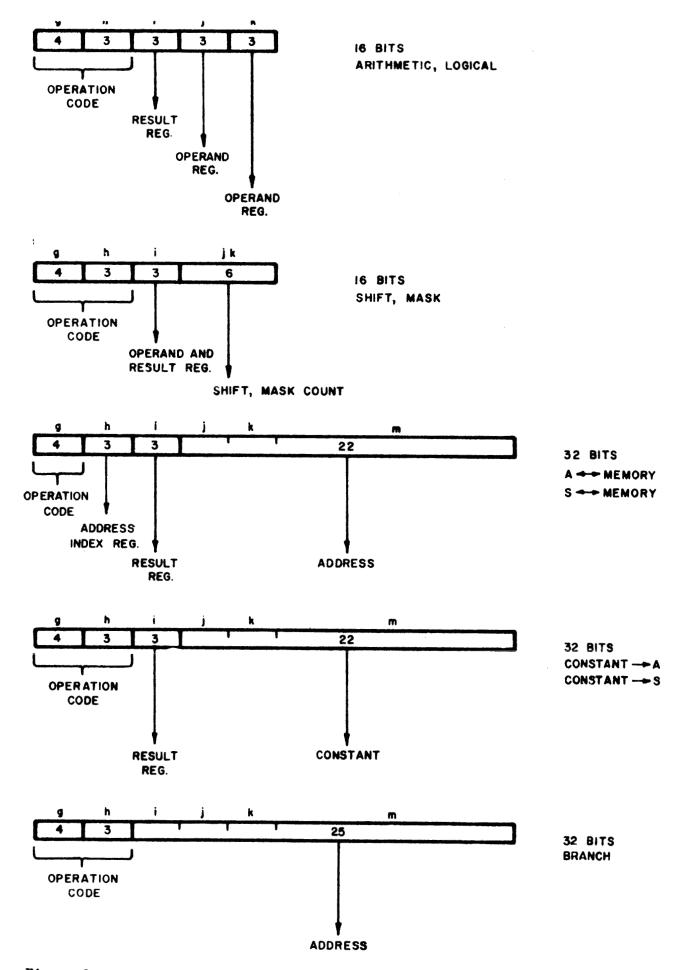

| Figure | 3. | Instruction formats       | • | • | • • | • | • | • | • | • | • | • | • | • | • | • | 8  |

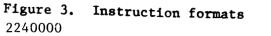

| Figure | 4. | Data formats              | • | • | •   | • | • | • | • | • | • | • | • | • | • | • | 10 |

#### Introduction

The Cray Research CRAY-1 computer is a powerful general purpose computer incorporating vector capabilities and a large, fast bi-polar memory. Vector processing provides result rates greatly exceeding the result rates of conventional scalar processing. The benefits of vector processing are visible even for short vectors. This manual introduces the characteristics of the CRAY-1 and describes the <u>CRAY-1</u> assembly language (CAL).

# Summary of machine characteristics

- 64-bit word

- 2's complement arithmetic

- scalar and vector processing modes

- 12 fully-segmented functional units

- eight 24-bit A registers

- sixty-four 24-bit B registers

- eight 64-bit S registers

- sixty-four 64-bit T registers

- eight 64-element V registers, 64 bits per element

- 4 instruction buffers of 64 parcels each

- 12.5 nanosecond clock period

- 1,048,576 words of bi-polar memory (64 bits and one parity bit) arranged in 16 banks

- 4 clock period bank cycle time

- 1 word/clock period transfer rate to B, T and V registers

- 1 word/two clock periods transfer rate to A and S registers

- 4 words/clock period transfer rate to instruction parcel buffers

- 12 full-duplex I/O channels

#### Principal operating registers

#### <u>A registers</u>

The eight 24-bit A registers are primarily used as address registers for memory references and as index registers. They are individually designated by the symbols AO, Al, A2, A3, A4, A5, A6 and A7. Data flows between these registers and the B, S and VL registers. Data may be directly transferred between the A registers and memory.

# **B** registers

The sixty-four 24-bit B registers provide rapid-access temporary storage for the A registers. They are individually designated by the symbols B0, B1, B2, ..., B77. Data may be directly transferred between the B registers and memory.

A

#### <u>S</u> registers

The eight 64-bit S registers are the principal scalar registers for the CPU. They are individually designated by the symbols SO, S1, S2, S3, S4, S5, S6 and S7. These registers serve as source and destination registers in scalar arithmetic and logical instructions. They may also furnish one operand in vector instructions. Data flows between these registers and the A, T, V, and VM registers. Data may be directly transferred between the S registers and memory.

# <u>T</u> registers

The sixty-four 64-bit T registers provide rapid-access temporary storage for the S registers. They are individually designated by the symbols T0, T1, T2, . . .,T77. Data may be directly transferred between the T registers and memory.

# V registers

The eight 64-element V registers are the operating registers for vector computations. Each element is 64 bits. The V registers are individually designated by the symbols VO, V1, V2, V3, V4, V5, V6 and V7. These registers serve as source and destination registers in vector arithmetic and logical instructions. Data flows between these registers and the S registers. Data may be directly transferred between the V registers and memory.

## VL register

The 7-bit VL register specifies the vector length. Vector computations are performed on vectors of the length specified by the contents of VL.

#### VM register

The 64-bit VM register contains a vector mask to control register selection in the vector merge instructions (146-147). Each bit of the VM register corresponds to a vector element.

## P register

The 24-bit P register specifies the parcel address of the current program instruction. The high order 22 bits specify a memory address and the low order 2 bits specify the parcel number.

Figure 1. Registers block diagram

|       | 16 | 24                              | 24  |

|-------|----|---------------------------------|-----|

|       |    | Ρ                               | AO  |

| + 1   |    | BA I                            | A I |

| + 2   |    | LA <sup>IO</sup> M <sup>3</sup> | A2  |

| + 3   |    | XA VL 7 FLAGS                   | A3  |

| • • □ |    |                                 | A4  |

| + 5   |    |                                 | A5  |

| + 6   |    |                                 | AG  |

| + 7   |    |                                 | A7  |

| + 8   |    | SO                              |     |

| +9    |    | <b>S</b> I                      |     |

| + 10  |    | 52                              |     |

|       |    | \$3                             |     |

| + 12  |    | <b>\$4</b> ·                    |     |

| + 13  |    | \$5                             |     |

| + 14  |    | \$6                             |     |

| + 15  |    | \$7                             |     |

#### FLAGS

#### Bit\*

- 31 Console Interrupt

- 32 RTC Interrupt

- 33 Floating Point Error (Set on Scalar Reference Only)

- 34 Operand Range

- 35 Program Range

- 36 Storage Parity

- 37 I/O Interrupt

- 38 Error Exit

- 39 Normal Exit

- \* Bit position from left of word

Figure 2. Exchange package 2240000

#### MODES

# Bit\*

- 31 Interrupt on Floating Point

- 32 Interrupt on Storage Parity

- 33 Monitor Mode

- P = Program Address

- BA = Base Address

- LA = Limit Address

- XA = Exchange Address

# VL = Vector Length

4

## Supporting registers

The CPU contains a number of registers which support the operating registers in the execution of programs. These registers are loaded with new information during the execution of an exchange sequence. The information is not altered during the execution interval for an exchange package. These registers are listed below with a description of the individual function performed.

# **BA** register

This 18-bit register holds the base address during the execution interval for each exchange package. The contents of this register is interpreted as the upper 18 bits of a 22-bit memory address. The lower 4 bits of the address are assumed zero. Absolute memory addresses are formed by adding (BA)\*16 to the relative address specified by the CPU instructions.

# LA register

This 18-bit register holds the limit address during the execution interval for each exchange package. The contents of this register is interpreted as the upper 18 bits of a 22-bit memory address. The lower 4 bits of the address are assumed zero. The BA and LA registers together provide memory protection. No memory references may be made below BA nor at or above LA. Such a reference will cause the program or operand range flag to be set and the execution interval of the exchange package will be terminated.

## XA register

This 8-bit register holds the upper eight bits of a 12-bit exchange address during the execution interval for each exchange package. The low order 4 bits of the exchange address are assumed zero.

When the execution interval terminates, the exchange operation exchanges the contents of the registers with the contents of the exchange package at (XA)\*16 in memory. The exchange operation saves the contents of the A, S, P, and VL registers and the supporting registers BA, LA, XA, M and F.

# F register

This 9-bit register contains flags which are set to indicate the conditions causing an exchange operation. The interrupt conditions are:

| <ul> <li>Normal exit</li> <li>Error exit</li> <li>I/O interrupt</li> <li>Storage parity</li> </ul> | <ul> <li>Operand range</li> <li>Floating point overflow<br/>(scalar only)</li> <li>External clock interrupt</li> </ul> |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| - Program range                                                                                    | - Console interrupt                                                                                                    |

## <u>M</u> register

This 3-bit register specifies the modes for generation of interrupts. All interrupts are inhibited when the monitor mode bit is set. Interrupts on storage parity errors are enabled when the storage parity mode bit is set. Interrupts on scalar floating point overflow are enabled when the floating point mode bit is set.

# Input/Output

There are twenty-four I/O channels, of which twelve are input channels and twelve are output channels. The channels are assigned the numbers 2 through 25. The channels are divided into four groups as follows:

| Group | 1 | Input channels  | 2, | 6, | 10, | 14, | 18, | 22 |

|-------|---|-----------------|----|----|-----|-----|-----|----|

| Group | 2 | Output channels | 3, | 7, | 11, | 15, | 19, | 23 |

| Group | 3 | Input channels  | 4, | 8, | 12, | 16, | 20, | 24 |

| Group | 4 | Output channels | 5, | 9, | 13, | 17, | 21, | 25 |

Each input channel consists of a data channel (16 data bits and 3 control bits), a 64-bit assembly register, a current address (CA) register, and a channel limit address (CL) register. Each input channel can cause a CPU interrupt condition when the current address equals the limit address register value or when the input device sends a disconnect.

Each output channel consists of a data channel (16 data bits and 3 control bits), a 64-bit disassembly register, a current address (CA) register, and a channel limit address (CL) register. Each output channel can cause a CPU interrupt condition when the current address equals the limit address register value. A disconnect is sent on the output channel after the last word of a record is sent and acknowledged.

## Comparison of scalar and vector processing

Scalar instructions apply a function to one or two operands in registers and enter the result into a register. The addition of two integers in S1 and S2, entering the sum into S3, is an example of a scalar instruction. Vector instructions apply a function to sets of operands called vectors. Suppose one wanted to perform several additions like the one above. One could execute a small loop which would perform one addition per pass, saving S3 sums as they are generated. Alternatively, one could enter the addends into elements of one V register and the augends into elements of another V register and then execute a single vector addition instruction. The set of addends, the set of augends, and the set of sums are vectors. Vector processing provides much higher result rates than can be obtained by conventional scalar processing.

#### Functional units

There are twelve functional units in the computation section of the CPU. Each is a specialized unit implementing algorithms for a portion of the instructions. Each unit is independent of the other units and a number of functional units may be in operation at the same time. A functional unit receives operands from registers and delivers the result to a register when the function has been performed. There is no information retained in a functional unit for reference in subsequent instructions. These units operate essentially in threeaddress mode with very limited source and destination addressing.

Three functional units provide 24-bit results to the A registers only:

integer addinteger multiplypopulation count

Three functional units provide 64-bit results to the S registers only:

integer addshiftlogical

Three functional units provide 64-bit results to the V registers only:

integer add

shift

logical

Three functional units provide 64-bit results to either the S or V registers:

floating addfloating multiplyreciprocal approximation

All functional units have one clock period segmentation. This means that the information arriving at the unit, or moving within the unit, is captured and held in a new set of registers at the end of every clock period. It is therefore possible to start a new set of operands for unrelated computation into a functional unit each clock period even though the unit may require more than one clock period to complete the calculation. All functional units perform their algorithms in a fixed amount of time. No delays are possible once the operands have been delivered to the unit. Functional units servicing the vector instructions produce one result per clock period.

## Instruction formats

Figure 3 illustrates the five instruction formats for the CRAY-1. Each instruction is either a one-parcel (16-bit) instruction or a two-parcel (32-bit) instruction. Two-parcel instructions may begin in the fourth and last parcel position within a word and end in the first parcel position of the next word. The assembler lists a parcel address as a word address followed by a one-character alphabetic (a-d) parcel identifier.

8

Α

#### Special register values

SO and AO provide special values when they are designated in the j or k portions of an instruction. In these cases the special value is used as the operand and the contents of SO or AO is ignored. If an SO or AO operand is designated in the i portion of an instruction, the actual contents of SO or AO is used as the operand. The instruction descriptions enumerate the uses of the special register values where they are meaningful.

| register        | value |

|-----------------|-------|

| Ai,i=0          | AO    |

| Aj,j=0          | 0     |

| Ak,k=0          | 1     |

| Si,i=0          | S0    |

| Sj,j=O          | 263   |

| Sk <b>,k=</b> 0 | 263   |

#### Instruction buffers

There are four instruction buffers each consisting of sixty-four 16-bit registers. All instructions are executed from the instruction buffers. An instruction buffer supplies instructions to the next instruction parcel (NIP) and the current instruction parcel (CIP) registers. Associated with each instruction buffer is a base address register that specifies the high order 18 bits of the parcel addresses contained in the instruction buffer. The base address registers are scanned each clock period. If the high order 18 bits of the P register matches one of the base addresses, the proper instruction is selected from the instruction buffer and sent to the NIP register. The instruction is moved to the CIP register for execution. The second parcel of a 2-parcel instruction resides in the NIP register when the instruction issues.

When the high order 18 bits of the P register do not match any instruction buffer base address, an "out of buffer" condition exists and instructions are read to an instruction buffer from memory. When an "out of buffer" condition occurs, the instruction buffer that receives the instruction is determined by a 2-bit counter. Each occurrence of an "out of buffer" condition causes the counter to be incremented. The first four instruction parcels in an instruction buffer are always from bank 0, however, the first parcels read into an instruction buffer always include the parcel specified by the contents of the P register.

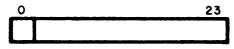

#### Data formats

Figure 4 illustrates the data formats for integers and floating point quantities. The range for floating point quantities is  $\begin{bmatrix} 10^{-5000} & 10^{2500} \end{bmatrix}$ . Normalized floating point quantities are expressed as  $z = y + 2^x$  where y = 0 or  $\frac{1}{2} \le y \le 1$  and  $-40000_8 \le x \le 20000_8$ . The exponent of x is expressed in excess-40000 notation. The exponent of a floating point quantity is obtained by adding 40000 to the true exponent. Overflow is indicated by an exponent exceeding  $57777_8$ .

SIGNED MAGNITUDE FLOATING POINT (64 BITS)

SIGN

2's COMPLEMENT INTEGER (24 BIT)

### CAL language structure

# Statement format

A CAL language source program consists of a sequence of symbolic machine instructions, pseudo instructions and comment lines. Except for comment lines, each statement consists of a location field, a result field, an operand field, and a comments field. Each field is terminated by one or more blank characters. Statement format is essentially free field.

Statements are 80 column lines. When punched on cards, each card is considered a line. Information beyond column 72 is not interpreted by CAL but does appear on the assembly listing. Thus, columns 73-80 can be used for additional comments or sequencing.

#### Location field

The location field entry begins in column one or two of a new statement line and is terminated by a blank. If columns one and two are blank, the location field has no entry.

# Result field

If the location field is blank, the result field can begin in column three. If the location field is nonblank, the result field begins with the first nonblank character following the location field and is terminated by one or more blanks. The result field is blank if there are no nonblank characters between the location field and column 35.

# Operand field

The contents of the result field determines if any entry is required in the operand field. The operand field begins with the first nonblank character following the result field and is terminated by one or more blanks. It is blank if there are no nonblank characters between the result field and column 35.

# Comments field

Comments are optional and begin with the first nonblank character following the operand field, or, if the operand field is missing, begin no earlier than column 35.

# Coding conventions

The following coding convention should be adopted to assure uniformity of all CRAY-1 systems code:

| Column | Contents                             |  |  |  |  |

|--------|--------------------------------------|--|--|--|--|

| 1      | Asterisk (comments statement only)   |  |  |  |  |

| 1-8    | Location field entry, left-justified |  |  |  |  |

| 9      | Blank                                |  |  |  |  |

| 10-18  | Result field entry, left-justified   |  |  |  |  |

| 19     | Blank                                |  |  |  |  |

| 20-34  | Operand field entry, left-justified  |  |  |  |  |

| 35     | Beginning of comments                |  |  |  |  |

#### Comments statement

A comments statement is designated by either an asterisk in column 1 or by blanks in columns 1-34. Comments statements are listed in assembler output but have no other effect on assembly.

#### Lower case in comments

Since the standard keypunch requires multipunching of lower case characters, an escape character is provided to indicate that succeeding alphabetic characters (A-Z) are to be converted to lower case. The conversion is performed only for comments statements and comments fields. Conversion is terminated by a subsequent occurrence of the escape character, which may be on a different card, or by the end of the program. When in lower case mode, a single alphabetic character may be capitalized by prefixing the capitalization character. The capitalization character has no effect if not followed by an alphabetic character.

|                          | <u>character</u> | card code | ASCII code |

|--------------------------|------------------|-----------|------------|

| Escape character         | SUB              | 7-8-9     | 032        |

| Capitalization character | EOT              | 7-9       | 004        |

#### Symbols

A symbol is a string of 1-8 characters that defines a value and its associated attributes. The first character must be alphabetic (A-Z), @ or \$. Second and successive characters may also be digits (0-9) or =. A symbol may have a word address or a parcel address attribute, or neither of these. A symbol is a parcel address if it appears in the location field of an instruction. A symbol is a word address if it appears in the location field of a CON, BSS, or BSSZ pseudo instruction. The "=" statement can be used to define a symbol with either attribute.

# Special element, \*

The use of the special element \* in an expression causes the assembler to replace it with the current value of the location counter.

# "P." prefix

A symbol or constant may be prefixed by a "P." to specify the attribute of parcel address. If a symbol, <u>sym</u>, has the attribute of word address, the value of P.<u>sym</u> is the value of <u>sym</u> multiplied by four. A "P." prefix to a symbol with neither word nor parcel address attributes or to a constant does not cause the value to be multiplied by four, but it can be used to assign the parcel address attribute to a symbol being defined by an "=" statement.

# "W." prefix

A symbol or constant may be prefixed by "W." to specify the attribute of word address. If a symbol, <u>sym</u>, has the attribute of parcel address, the value of W.<u>sym</u> is the value of <u>sym</u> divided by four. A "W." prefix to a symbol with neither word nor parcel address attributes or to a constant does not cause the value to be divided by four, but it can be used to assign the word address attribute to a symbol being defined by an "="

#### Expressions

Expressions are evaluated from left to right without regard for operator (+, -, \* and /) precedence. Expressions in branch instructions (006-017) must not evaluate to type "word address". Expression elements may be one of the following forms:

\* symbol octal constant O'nnnn (nnnn, an octal constant) D'nnnn (nnnn, a decimal constant) A'cccc' (cccc, a character string) 'cccc'

A'cccc' or 'cccc' left-justifies the character string in a 64-bit field with blank fill. A suffix may be used to specify an alternate justification or fill: H - same as no suffix, L - left-justified, zero fill, or R - right-justified, zero fill. An apostrophe in a character string is represented as two apostrophes. A null expression is given the value zero.

#### CPU register designation

A, S, and V registers are designated by suffixing a single octal digit, n (An, Sn, Vn). B and T registers are designated by suffixing one or two octal digits (Bnn, Tnn). A symbol may be used in place of a B or T register number if the register name and number are separated by a period. The symbol must have been previously defined. For example,

$\begin{array}{rcl} \text{RTNADDR} &= & 14 \\ & & \text{J} & \text{B}.\text{RTNADDR} \\ \text{accomplishes the same thing as} \\ & & \text{J} & \text{B14} & . \end{array}$

#### Pseudo instructions

Three pseudo instructions are required for an assembly: IDENT, ENTRY, and END. IDENT must be the first source statement. END signals the termination of source statements for a program. Statements preceding the first IDENT or between a succeeding END and subsequent IDENT are interpreted as comments.

# ABS

The ABS pseudo instruction specifies that the program is absolute. This pseudo must precede any BSS, BSSZ, CON, = or instruction. It has no real purpose for the NOVA CAL assembler and may be omitted, but it is implemented to facilitate the eventual relocatable module capability.

## Example:

| location | result | operand | comments |

|----------|--------|---------|----------|

| 1        | 10     | 20      | 35       |

|          | ABS    |         |          |

# BSS

The BSS pseudo instruction causes a block of storage to be reserved. The location counter is first rounded to the next word boundary (force upper), and then the number of words specified by the operand field expression is reserved. Unused parcels are padded with pass instructions (Sl Sl&Sl). A location field symbol, if present, is assigned the value of the current word address after the force upper occurs.

| location | result     | operand          | comments                                |

|----------|------------|------------------|-----------------------------------------|

| 1        | 10         | 20               | 135                                     |

|          | BSS<br>BSS | 4<br>W.*+7/10*10 | Round to 10 <sub>8</sub> -word boundary |

## BSSZ

The BSSZ pseudo instruction causes a block of zero storage to be reserved. The location counter is first rounded to the next word boundary (force upper), and then the number of zero words specified by the operand field expression is reserved. A location field symbol, if present, is assigned the value of the current word address after the force upper occurs.

## Example:

| location | result | operand | comments |

|----------|--------|---------|----------|

| 1        | 10     | 20      | 35       |

|          | BSSZ   | 177     | 1        |

# CON

The CON pseudo instruction generates a full word of binary data. This pseudo always forces upper. A location field symbol, if present, is assigned the value of the current word address after the force upper occurs.

#### Example:

| location | result | operand | comments |

|----------|--------|---------|----------|

| 1        | 10     | 20      | 135      |

|          | CON    | 7777017 |          |

#### EJECT

The EJECT pseudo instruction causes the next listing line to appear on a new page. The EJECT pseudo itself is not listed. The EJECT pseudo has no effect when the E global switch is selected.

#### Example:

| location | result | operand | comments |

|----------|--------|---------|----------|

| 1        | 10     | 20      | 35       |

|          | EJECT  |         |          |

#### END

The END pseudo instruction indicates the end of the program. Subsequent cards, if any, are assumed to be part of the next program.

| location | result | operand | comments |

|----------|--------|---------|----------|

| 1        | 10     | 20      | 35       |

|          | END    |         |          |

# ENTRY

The ENTRY pseudo instruction specifies an entry point of the program. Only one ENTRY pseudo is permitted by the initial CAL assembler. The entry point name is specified in the operand field and must subsequently appear in the location field of an instruction or "=" pseudo instruction.

Example:

| location | result | operand | comments |

|----------|--------|---------|----------|

| 1        | 10     | 20      | 35       |

|          | ENTRY  | EPTNME  | 1        |

# \_

The "=" pseudo instruction defines the symbol in the location field as having the value and attribute indicated by the expression in the operand field. Any symbol in the expression must be previously defined. If the expression is erroneous, CAL does not define the location symbol but flags an error.

Example:

| location | result | operand   | comments |

|----------|--------|-----------|----------|

| 1        | 10     | 20        | 35       |

| SYMB     | =      | A*B+100/4 |          |

# IDENT

The name of the program is specified in the operand field of the IDENT pseudo instruction. The name must be 1-8 characters, of which the first must be alphabetic (A-Z), @ or \$. Second and successive characters may also be digits (0-9) or =. The name appears in the listing heading and in the program descriptor table (PDT) of the absolute module.

Example:

| location | result | operand | comments |

|----------|--------|---------|----------|

| 1        | 10     | 20      | 135      |

|          | IDENT  | РМЈ     |          |

# LIST

The LIST pseudo instruction controls the listing. If the operand field is empty the listing is suppressed until encountering another LIST pseudo with a non-empty operand field, or until the end of the program.

| location | result | operand | comments |

|----------|--------|---------|----------|

| 1        | 10     | 20      | 35       |

|          | LIST   | DN      |          |

The ORG pseudo instruction specifies the origin of the program. This pseudo must precede any BSS, BSSZ, CON, = or instruction. The origin is specified in the operand field. If omitted, an origin of zero is assumed.

| ſ | location | result | operand | comments |

|---|----------|--------|---------|----------|

|   |          | 10     | 20      | 35       |

| Γ |          | DRG    | 0'100   |          |

#### CPU instructions

#### - 000 ERR Error Exit

This instruction is treated as an error condition and an exchange jump occurs. The contents of the instruction buffers are voided by the exchange jump. If not in monitor mode, the error exit flag in the F register is set. If in monitor mode, no bits are set in the F register.

All instructions issued prior to this instruction are run to completion. When all results have arrived at the operating registers as a result of previously issued instructions, an exchange jump occurs to the exchange package designated by the contents of the XA register. The program address stored in the exchange package on the terminating exchange jump is advanced one count from the address of the error exit instruction. The error exit instruction is not intended for use in user program code. Its purpose is to halt execution of an incorrectly coded program which jumps into an unused area of memory or into a data area.

# Example:

| Code Generated | location | result | operand | comments |

|----------------|----------|--------|---------|----------|

|                | 1        | 10     | 20.     | 35       |

| 000000         |          | ERR    |         |          |

| - 001 CA,Aj Ak | Set the channel (Aj) current address to (Ak) and     |

|----------------|------------------------------------------------------|

|                | begin the I/O sequence                               |

| CL,Aj Ak       | Set the channel (Aj) limit address to (Ak)           |

| CI,Aj          | Clear the channel (Aj) interrupt flag and error flag |

| XA Aj          | Enter the XA register with (Aj)                      |

| RT Sj          | Enter the real time clock register with (Sj)         |

This instruction performs specialized functions useful to the operating system. The instruction is treated as a pass instruction if not in monitor mode or if the i designator is 5, 6 or 7.

When the i designator is 0, 1 or 2, the instruction controls the operation of the I/O channels. Each channel has two registers that direct the channel activity. The CA register contains the address of the current channel word. The CL register specifies the limit address. In programming the channel, the CL register is initialized and setting CA activates the channel. As the transfer continues CA is incremented toward CL. When CA=CL the transfer is complete. When the j designator is 0 or when the contents of Aj is less than 2 or greater than 25, these functions are executed as pass instructions. When the k designator is 0, CA or CL is set to 1.

| Code Generated | locati | on result | operand | comments |

|----------------|--------|-----------|---------|----------|

|                | 1      | 10        | 20.     | 35       |

| 001035         |        | CA,A3     | A5      |          |

| 001134         | ]      | CL,A3     | A4      |          |

| 001210         | l      | CI,A1     |         |          |

When the i designator is 3, the instruction causes the exchange address (XA) register to be set to the contents of Aj. When the j designator is zero, the XA register is cleared. A monitor program activates a user job by initializing the XA register with the address of the user job's exchange package and then executing a normal exit (004).

Examples:

| Code Generated | locati | on result | operand | comments  |

|----------------|--------|-----------|---------|-----------|

|                | 1      | 10        | 20      | 35        |

| 001350         |        | XA        | A5      |           |

| 001420         |        | RT        | S2      |           |

| 001400         |        | RT        | SO      | clear RTC |

- 002 VL Ak Transmit Ak to VL

This instruction enters the vector length (VL) register with a value determined by the contents of Ak. The low order seven bits of Ak are entered into the VL register. Vector instructions operate on vectors whose lengths are determined by subtracting one from the contents of VL; one plus the contents of the low order six bits of the result is the vector length. The maximum vector length of 64 can be achieved by setting the contents of Ak to zero or 64 before executing this instruction. When the k designator is zero, the vector length is set to one.

Examples:

| Code Generated | location | n result  | operand | comments |

|----------------|----------|-----------|---------|----------|

|                | 1        | 10        | 20      | 35       |

| 020200000100   |          | A2        | D'64    | NL = 64  |

| 002002         |          | VL        | A2      |          |

| 022100         |          | A1        | 0       | VL = 64  |

| 002001         |          | <b>VL</b> | A1      |          |

- 003 VM Sj Transmit Sj to VM

This instruction enters the vector mask (VM) register with the contents of Sj. The VM register is cleared if the j designator is zero. This instruction is used in conjunction with the vector merge instructions (146 and 147) where an operation is performed depending on the contents of VM.

| Code Generated | location r | esult | operand | comments |

|----------------|------------|-------|---------|----------|

|                | 1 1        | 0     | 20      | 35       |

| 003040         |            | /M    | S4      |          |

| 003000         |            | /M    | S0      | VM = 0   |

# - 004 EX Normal exit

This instruction causes an exchange jump. The contents of the instruction buffers are voided by the exchange jump. If not in monitor mode, the normal exit flag in the F register is set. All instructions issued prior to this instruction are run to completion. When all results have arrived at the operating registers as a result of previously issued instructions, an exchange jump occurs to the exchange package designated by the contents of the XA register. The program address stored in the exchange package is advanced one count from the address of the normal exit instruction. This instruction is used to issue a monitor request from a user program. The value of an optional operand field expression is inserted in the lower 9 bits of the instruction. This instruction.

Examples:

| Code Generated | location | result | operand | comments |

|----------------|----------|--------|---------|----------|

|                | 1        | 10     | 20      | 35       |

| 004000         |          | EX     |         | 1        |

| 004027         | I        | EX     | 27      |          |

- 005 J Bjk Branch to (Bjk)

This instruction sets the P register to the parcel address specified by the contents of Bjk, and execution continues at that address.

# Examples:

| Code Generated | location | result | operand           | comments     |

|----------------|----------|--------|-------------------|--------------|

|                | 1        | 10     | 20                | 135          |

| 005017         |          | J      | B17               |              |

| 005017         |          | J      | <b>B</b> .RTNADDR | (RTNADDR=17) |

- 006 J exp Branch to ijkm

This instruction sets the P register to the parcel address specified by the low order 24 bits of the ijkm field, and execution continues at that address. The high order bit of the ijkm field is ignored.

| Code Generated | location | result | operand | comments |

|----------------|----------|--------|---------|----------|

|                | 1        | 10     | 20      | 35       |

| 006 00002124ь  |          | J      | TAG1    |          |

| 006 00001752d  |          | JJ     | LDY3+1  |          |

| 006 00004530a  |          | J      | *+3     | i        |

#### - 007 R exp Return jump to ijkm

This instruction sets register BOO to the address of the following parcel. The P register is then set to the parcel address specified by the low order 24 bits of the ijkm field, and execution continues at that address. The high order bit of the ijkm field is ignored. The purpose of this instruction is to provide a return linkage for subroutine calls. The subroutine is entered via a return jump. The subroutine returns to the caller at the instruction following the call by executing a branch instruction on the contents of BOO (005).

Example:

| Code Generated | location | result | operand | comments |

|----------------|----------|--------|---------|----------|

|                | 1        | 10     | 20      | 35       |

| 007 00001142d  |          | R      | THELP   | 1        |

|   | 010 | JAL | exp | Branch | τo | 1]KM | 11 | AU=U          |

|---|-----|-----|-----|--------|----|------|----|---------------|

| - | 011 | JAN | exp | Branch | to | ijkm | if | A0 <b>≠</b> 0 |

| - | 012 | JAP | ехр | Branch | to | ijkm | if | A0 positive   |

| - | 013 | JAM | ехр | Branch | to | ijkm | if | A0 negative   |

These instructions test the contents of AO for the condition specified. If the condition is satisfied, the P register is set to the parcel address specified by the low order 24 bits of the ijkm field, and execution continues at that address. The high order bit of the ijkm field is ignored. If the condition is not satisfied, execution continues with the instruction following the branch instruction. If AO contains zero, it is considered positive.

| Code Generated | locatio | n result | operand | comments |

|----------------|---------|----------|---------|----------|

|                | 1       | 10       | 20      | 35       |

| 010 00002245b  |         | JAZ      | TAG3+2  |          |

| 011 00004520a  |         | JAN      | P.CON1  |          |

| 012 00002221c  |         | JAP      | TAG2    |          |

| 013 00002124Ь  |         | JAM      | TAG1    |          |

| - 014 JSZ | exp | Branch to ijkm if SO=O       |

|-----------|-----|------------------------------|

| - 015 JSN | exp | Branch to ijkm if SO≠O       |

| - 016 JSP | exp | Branch to ijkm if SO positiv |

| - 017 JSM | exp | Branch to ijkm if SO negativ |

These instructions test the contents of SO for the condition specified. If the condition is satisfied, the P register is set to the parcel address specified by the low order 24 bits of the ijkm field, and execution continues at that address. The high order bit of the ijkm field is ignored. If the condition is not satisfied, execution continues with the instruction following the branch instruction. If SO contains zero, it is considered positive.

#### Examples:

| Code Generated | locati | on result   | operand | comments |

|----------------|--------|-------------|---------|----------|

|                | 1      | 10          | 20      | 35       |

| 14 00002221c   |        | JSZ         | TAG2    |          |

| )15 00002124d  |        | <b>J</b> SN | TAG1+2  |          |

| 16 00004540d   |        | JSP         | *+3     |          |

| 017 00002367c  | •      | JSM         | TAG4    | 1        |

# - 020 Ai exp Transmit jkm to Ai Ai #exp

This two-parcel instruction enters the 22-bit quantity of the jkm field into Ai. The quantity is treated as a 22-bit positive integer; the upper bits of Ai are cleared. The assembler generates this instruction when no # symbol precedes the expression and the value of the expression exceeds 63. If all symbols in the expression have not been previously defined, this instruction is generated when the expression value is positive even though the value may be less than 64. When the # symbol precedes the expression, the expression is first evaluated and if the value is negative, it is complemented and the complemented value is stored in the jkm field. The complement is formed by changing all 1 bits to zero and all 0 bits to one. When the expression is positive, an 021 instruction is generated (see below).

| Code Generated | location | result | operand | comments  |

|----------------|----------|--------|---------|-----------|

|                | 1        | 10     | 20      | 135       |

| 020200000130   |          | A2     | 130     |           |

| 02030000021    |          | A3     | VAL+1   | 1         |

| 020401777777   |          | A4     | 1777777 |           |

| 020500051531   |          | A5     | A'SY'R  |           |

| 02060000000    |          | A6     | #MINUS1 | MINUS1=-1 |

# - 021 Ai exp Transmit jkm to Ai and complement Ai #exp

This two-parcel instruction enters the 22-bit quantity of the jkm field into Ai and complements the result. The complement is formed by changing all 1 bits to zero and all 0 bits to one. This instruction is used to enter a negative number into an A register. The assembler generates this instruction when the value of the expression is negative and no # symbol precedes the expression; the jkm field will contain the complement of the expression. When the # symbol precedes the expression, the expression is first evaluated and if the value is positive it is stored in the jkm field. When the expression is negative, an 020 instruction is generated (see above).

Examples:

| Code Generated      | location | result | operand | comments |

|---------------------|----------|--------|---------|----------|

|                     | 1        | 10     | 20      | 35       |

| 021200000010        |          | A2     | #10     |          |

| <b>02</b> 120000007 |          | A2     | -10     |          |

- 022 Ai exp Transmit jk to Ai

This one-parcel instruction enters the 6-bit quantity of the jk field into Ai. All symbols in the expression must be previously defined. If all symbols are not previously defined, an 020 instruction is generated even though the value may be less than 64.

Example:

| Code Generated | location | result | operand | comments |

|----------------|----------|--------|---------|----------|

|                | 1        | 10     | 20      | 135      |

| 022310         |          | A3     | 10      |          |

- 023 Ai Sj Transmit Sj to Ai

This instruction enters the low order 24 bits of Sj into Ai. Ai is cleared if the j designator is zero.

| Code Generated | location | result | operand | comments |

|----------------|----------|--------|---------|----------|

|                | 1        | 10     | 20      | 35       |

| 023410         |          | A4     | S1      |          |

# - 024 Ai Bjk Transmit Bjk to Ai

This instruction enters the contents of Bjk into Ai. A symbolic B register number must be previously defined.

Examples:

| Code Generated | location | result | operand          | comments |

|----------------|----------|--------|------------------|----------|

|                | 1        | 10     | 20               | 35       |

| 024517         |          | A5     | B17              |          |

| 024517         |          | A5     | <b>B.SVNTEEN</b> | i        |

# - 025 Bjk Ai Transmit Ai to Bjk

This instruction enters the contents of Ai into Bjk. A symbolic B register number must be previously defined.

Examples:

| Code Generated | location | result   | operand | comments |

|----------------|----------|----------|---------|----------|

|                | 1        | 10       | 20      | 35       |

| 025634         |          | B34      | A6      |          |

| 025634         |          | B.THRTY4 | A6      |          |

- 026 Ai PSj Population count of Sj to Ai

This instruction counts the number of one bits in Sj and enters the result into Ai. Ai is cleared if the j designator is zero.

Example:

| Code Generated | location | result | operand         | comments |

|----------------|----------|--------|-----------------|----------|

|                | 1        | 10     | 20 <sup>.</sup> | 35       |

| 026720         |          | A7     | PS2             | 1        |

- 027 Ai ZSj Leading zero count of Sj to Ai

This instruction counts the number of leading zeroes in Sj and enters the result into Ai. Ai is set to 64 if the j designator is zero.

| Code Generated | location | result | operand | comments |

|----------------|----------|--------|---------|----------|

|                | 1        | 10     | 20      | i35      |

| 027130         |          | A1     | ZS3     |          |

# - 030 Ai Aj+Ak Integer sum of Aj and Ak to Ai

This instruction forms the integer sum of Aj and Ak and enters the result into Ai. No overflow is detected. Ak is transmitted to Ai when the j designator is zero and the k designator is non-zero. One is transmitted to Ai when the j and k designators are both zero. (Aj)+1 is transmitted to Ai when the j designator is non-zero and the k designator is zero. The assembler allows alternate forms for this instruction when either j or k designator is zero.

Examples:

| Code Generated | locati | lon result | operand | comments       |

|----------------|--------|------------|---------|----------------|

|                | 1      | 10         | 20      | 35             |

| 030123         |        | A1         | A2+A3   |                |

| 030102         | ,      | A1         | A2      | (special form) |

| 030230         |        | A2         | A3+1    | (special form) |

- 031 Ai Aj-Ak Integer difference of Aj and Ak to Ai

This instruction forms the integer difference of Aj and Ak and enters the result into Ai. No overflow is detected. The negative of Ak is transmitted to Ai when the j designator is zero and the k designator is non-zero. -1 is transmitted to Ai when the j and k designators are both zero. (Aj)-1 is transmitted to Ai when the j designator is non-zero and the k designator is zero. The assembler allows alternate forms for this instruction when either j or k designator is zero.

Examples:

| Code Generated | locat | ion result | operand | comments       |

|----------------|-------|------------|---------|----------------|

|                | 1     | 10         | 20      | 35             |

| 031456         |       | A4         | A5-A6   |                |

| 031102         |       | A1         | -A2     | (special form) |

| 031450         |       | A4         | A5-1    | (special form) |

- 032 Ai Aj\*Ak Integer product of Aj and Ak to Ai

This instruction forms the integer product of Aj and Ak and enters the low order 24 bits of the result into Ai. No overflow is detected. Ai is cleared when the j designator is zero. Aj is transmitted to Ai when the k designator is zero and the j designator is non-zero.

| Code Generated | location | result | operand | comments |

|----------------|----------|--------|---------|----------|

|                | 1        | 10     | 20      | 135      |

| 032712         |          | A7     | A1*A2   |          |

| - 033 Ai | CI    | Channel number of highest priority interrupt |

|----------|-------|----------------------------------------------|

|          |       | request to Ai                                |

| Ai       | CA,Aj | Current address of channel (Aj) to Ai        |

| Ai       | CE,Aj | Error flag of channel (Aj) to Ai             |

This instruction enters channel status information into Ai. The j and k designators and the contents of Aj define the desired information. The channel number of the highest priority interrupt request is entered into Ai when the j designator is zero. The contents of Aj specifies a channel number when the j designator is nonzero. The value of the current address (CA) register for the channel is entered into Ai when the k designator is zero. The error flag for the channel is entered into the low order bit of Ai when the k designator is one. The high order bits of Ai are cleared. The error flag is cleared only by the 0012 instruction and is privileged to the monitor. Examples:

| Code Generated | locati | on result | operand | comments |

|----------------|--------|-----------|---------|----------|

|                | 1      | 10        | 20      | 35       |

| 033100         |        | A1        | CI      |          |

| 033230         |        | A2        | CA,A3   |          |

| 033341         |        | A3        | CE,A4   |          |

- 034 Bjk,Ai ,A0 Read (Ai) words starting at B register jk from memory starting at (A0)

This instruction is used to read the low order 24 bits of words from memory directly into the B registers. A0 contains the address in memory of the first word. The B register which is to receive the first word is specified by jk. Subsequent words are stored in consecutive B registers. Processing of the B registers is circular. B00 is processed after B77 if the count is not exhausted. The low order seven bits of (Ai) specify the number of words read. A0 in the operand field is optional.

| Code Generated   | locat | ion result     | operand  | comments |

|------------------|-------|----------------|----------|----------|

|                  | 1     | 10             | 20       | 35       |

| 034407<br>034407 |       | B7,A4<br>B7,A4 | ,A0<br>, |          |

- 035 ,A0 Bjk,Ai Store (Ai) words starting at B register jk to memory starting at (A0)

This instruction is used to store the B registers directly into memory. A0 contains the address in memory to receive the first word. The B register which is stored at the first address is specified by jk. Subsequent B registers are stored in consecutive words in memory. Processing of the B registers is circular. B00 is processed after B77 if the count is exhausted. The low order seven bits of (Ai) specify the number of words written. A0 in the operand field is optional.

# Examples:

| Code Generated            | location | result   | operand          | comments |

|---------------------------|----------|----------|------------------|----------|

|                           | 1        | 10       | 20               | 35       |

| 035 <b>52</b> 2<br>035522 |          | ,A0<br>, | B22,A5<br>B22,A5 |          |

# - 036 Tjk ,Ai ,A0 Read (Ai) words starting at T register jk from memory starting at (A0)

This instruction is used to read 64-bit words from memory directly into the T registers. A0 contains the address in memory of the first word. The T register which is to receive the first word is specified by jk. Subsequent words are stored in consecutive T registers. Processing of the T registers is circular. TOO is processed after T77 if the count is not exhausted. The low order seven bits of (Ai) specify the number of words read. A0 in the operand field is optional.

| Code Generated   | location | result         | operand | comments |

|------------------|----------|----------------|---------|----------|

|                  | 1        | 10             | 20.     | 35       |

| 036407<br>036407 |          | T7,A4<br>T7,A4 | ,A0     |          |

- 037 ,A0 Tjk,Ai Store (Ai) words starting at T register jk to memory starting at (A0)

This instruction is used to store the T registers directly into memory. AO contains the address in memory to receive the first word. The T register which is stored at the first address is specified by jk. Subsequent T registers are stored in consecutive words in memory. Processing of the T registers is circular. TOO is processed after T77 if the count is not exhausted. The low order seven bits of (Ai) specify the number of words written. AO in the operand field is optional.

Examples:

| Code Generated   | location | result   | operand          | comments |

|------------------|----------|----------|------------------|----------|

|                  | 1        | 10       | 20               | 35       |

| 037522<br>037522 |          | ,A0<br>, | T22,A5<br>T22,A5 |          |

- 040 Si exp Transmit jkm to Si Si #exp

This two-parcel instruction enters the 22-bit quantity of the jkm field into Si. The quantity is treated as a 22-bit positive integer; the upper bits of Si are cleared. The assembler generates this instruction when no # symbol precedes the expression and the value of the expression is positive. When the # symbol precedes the expression, the expression is first evaluated and if the value is negative, it is complemented and the complemented value is stored in the jkm field. The complement is formed by changing all 1 bits to zero and all 0 bits to one. When the expression is positive, an 041 instruction is generated (see below).

| Code Generated | location | result | operand | comments  |

|----------------|----------|--------|---------|-----------|

|                | 1        | 10     | 20      | 35        |

| 040200000130   |          | S2     | 130     |           |

| 040300000021   |          | S3     | VAL+1   |           |

| 040401777777   |          | S4     | 1777777 |           |

| 040500051531   |          | S5     | A'SY'R  |           |

| 040600000000   |          | S6     | #MINUS1 | MINUS1=-1 |

# - 041 Si exp Transmit jkm to Si and complement Si #exp

This two-parcel instruction enters the 22-bit quantity of the jkm field into Si and complements the result. The complement is formed by changing all 1 bits to zero and all 0 bits to one. This instruction is used to enter a negative number into an S register. The assembler generates this instruction when the value of the expression is negative and no # symbol precedes the expression; the jkm field will contain the complement of the expression value. When the # symbol precedes the expression is first evaluated and if the value is positive, it is stored in the jkm field. When the expression is negative, an 040 instruction is generated (see above).

Examples:

| Code Generated | location | result | operand  | comments |

|----------------|----------|--------|----------|----------|

|                | 1        | 10     | 20       | 35       |

| 04120000000    |          | S2     | -1       |          |

| 04130000002    |          | S3     | #2       |          |

| 041401777776   |          | S4     | -1777777 |          |

| 04140000003    |          | S4     | #VAL2    | (VAL2=3) |

# - 042 Si <exp Form ones mask in Si from the right Si #>exp

This instruction is used to generate a mask of ones from the right. The assembler evaluates the expression to determine the mask length. If the # symbol precedes the expression the mask length is 64 minus the expression value. All symbols in the expression must be previously defined. The assembler stores 64 minus the mask length in the jk field of the instruction. The mask length must be a positive integer not exceeding 64. If the mask length is zero, an 043 instruction is generated.

| Code Generated | location | result | operand                        | comments       |

|----------------|----------|--------|--------------------------------|----------------|

|                | 1        | 10     | 20                             | 35             |

| 042273         |          | S2     | <5                             |                |

| 042273         |          | S2     | #>73                           |                |

| 042366         |          | S3     | <d'10< td=""><td></td></d'10<> |                |

| 042400         |          | S4     | <100                           | 1              |

| 043500         |          | S5     | <0                             |                |

| 042677         |          | S6     | 1                              | (special form) |

| - | 043 | Si | >exp                                                                                                   | Form | one <b>s</b> | mask | in | Si | from | the | left |  |

|---|-----|----|--------------------------------------------------------------------------------------------------------|------|--------------|------|----|----|------|-----|------|--|

|   |     | Si | # <exp< th=""><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></exp<> |      |              |      |    |    |      |     |      |  |

This instruction is used to generate a mask of ones from the left. The assembler evaluates the expression to determine the mask length. If the # symbol precedes the expression the mask length is 64 minus the expression value. All symbols in the expression must be previously defined. The assembler stores the mask length in the jk field of the instruction. The mask length must be a positive integer not exceeding 64. If the mask length is 64, an 042 instruction is generated.

Examples:

| Code Generated | location result | operand       | comments |

|----------------|-----------------|---------------|----------|

|                | 1 10            | 20            | 35       |

| 043205         | S2              | >5            |          |

| 043205         | S2              | #<73          |          |

| 043312         | 53              | >D'10         | i        |

| 042400         | S4              | >100          |          |

| 043500         | S5              | <b>&gt;</b> 0 |          |

| 043600         | 56              | 0             | i        |

- 044 Si Sj&Sk Logical product of Sj and Sk to Si

This instruction forms the logical product (AND) of Sj and Sk and enters the result into Si. Bits of Si are set to 1 when the corresponding bits of Sj and Sk are 1 as in the following example:

$$(Sj) = 1100$$

$(Sk) = 1010$

$(Si) = 1000$

Sj is transmitted to Si if the j and k designators have the same nonzero value. Si is cleared if the j designator is zero. The sign bit of Sj is extracted into Si if the j designator is non-zero and the k designator is zero.

| Code Generated                       | locati | on result            | operand                          | comments                               |

|--------------------------------------|--------|----------------------|----------------------------------|----------------------------------------|

|                                      | 1      | 10                   | 20.                              | 35                                     |

| 044234<br>044655<br>044307<br>044160 |        | S2<br>S6<br>S3<br>S1 | S3&S5<br>S5&S5<br>S0&S7<br>S6&S0 | S5 to S6<br>clear S3<br>get sign of S6 |

- 045 Si #Sk&Sj Logical product of Sj and complement of Sk to Si

This instruction forms the logical product (AND) of Sj and the complement of Sk and enters the result into Si. Bits of Si are set to 1 when the corresponding bits of Sj and the complement of Sk are 1 as in the following example:

> (Sj) = 1100(Sk) = 1010(Si) = 0100

Si is cleared if the j and k designators have the same value or if the j designator is zero. Sj, with the sign bit cleared, is transmitted to Si if the j designator is non-zero and the k designator is zero.

Examples:

| Code Generated | location | result | operand | comments       |

|----------------|----------|--------|---------|----------------|

|                | 1        | 10     | 20      | 35             |

| 045271         |          | S2     | #S1&S7  |                |

| 045433         |          | S4     | #S3&S3  | clear S4       |

| 045506         |          | S5     | #S6&S0  | iclear S5      |

| 045670         |          | S6     | #S0&S7  | clear sign bit |

- 046 Si Sj~Sk Logical difference of Sj and Sk to Si

This instruction forms the logical difference (exclusive OR) of Sj and Sk and enters the result into Si. Bits of Si are set to 1 when the corresponding bits of Sj and Sk are different as in the following example:

> (Sj) = 1100(Sk) = 1010(Si) = 0110

Si is cleared if the j and k designators have the same non-zero value. Sk is transmitted to Si if the j designator is zero and the k designator is non-zero. The sign bit of Sj is complemented and the result is transmitted to Si if the j designator is non-zero and the k designator is zero.

| Code Generated | location r | esult | operand | comments     |

|----------------|------------|-------|---------|--------------|

|                | 1          | 0     | 20      | 35           |

| 046123         |            | s1    | S2~S3   |              |

| 046455         |            | S4    | \$5~\$5 | clear S4     |

| 046506         |            | \$5   | 50-56   | iS6 to S5    |

| 046770         |            | \$7   | 57~50   | !toggle sign |

- 047 Si #Sj\Sk Logical difference of Sk and Sj complement to Si

This instruction forms the logical difference (exclusive OR) of Sk and the complement of Sj and enters the result into Si. Bits of Si are set to 1 when the corresponding bits of Sj and Sk are the same, as in the following example:

$$(Sj) = 1100$$

$(Sk) = 1010$

$(Si) = 1001$

Si is set to all ones if the j and k designators have the same nonzero value. The complement of Sk is transmitted to Si if the j designator is zero and the k designator is non-zero. The assembler allows a special form for this case, as shown in the example below. All bits except the sign bit of Sj are complemented and the result is transmitted to Si if the j designator is non-zero and the k designator is zero.

Examples:

| Code Generated | location | result | operand | comments       |

|----------------|----------|--------|---------|----------------|

|                | 1        | 10     | 20      | !35            |

| 047345         |          | S3     | #S4\S5  |                |

| 047607         |          | S6     | #S7     | (special form) |

#### - 050 Si Sj!Si&Sk Scalar merge

This instruction merges the contents of Sj with Si depending on the ones mask in Sk. The result is defined by (Sj&Sk)!(Si&#Sk) as in the following example:

| (Sk) | = | 11110000 |

|------|---|----------|

| (S1) | = | 11001100 |

| (Sj) | = | 10101010 |

| (Si) | = | 10101100 |

This instruction is intended for merging portions of 64-bit words into a composite word. Bits of Si are cleared when the corresponding bits of Sk are 1 if the j designator is zero and the k designator is non-zero. The sign bit of Sj replaces the sign bit of Si if the j designator is non-zero and the k designator is zero. The sign bit of Si is cleared if the j and k designators are both zero.

| Code Generated | locatio | n result | operand  | comments |

|----------------|---------|----------|----------|----------|

|                | 1       | 10       | 20       | 35       |

| 050123         |         | S1       | S2:S1&S3 |          |

| 050760         | I       | S7       | S6:S7&S0 |          |

This instruction forms the logical sum (inclusive OR) of Sj and Sk and enters the result into Si. Bits of Si are set when one of the corresponding bits of Sj and Sk is set, as in the following example:

$$(Sj) = 1100$$

$(Sk) = 1010$

$(Si) = 1110$

Sj is transmitted to Si if the j and k designators have the same non-zero value. Sk is transmitted to Si if the j designator is zero and the k designator is non-zero. The assembler allows a special form for this case, as in the example below. Sj, with the sign bit set to 1, is transmitted to Si if the j designator is non-zero and the k designator is zero. A ones mask consisting of only the sign bit is entered into Si if the j and k designators are both zero.

#### Examples:

| Code Generated                       | location | result         | operand                       | comments        |

|--------------------------------------|----------|----------------|-------------------------------|-----------------|

|                                      | 1        | 10             | 20.                           | 35              |

| 051472<br>051366<br>051701<br>051701 |          | S4<br>S3<br>S7 | \$7!\$2<br>\$6!\$6<br>\$0!\$1 |                 |

| 031701                               |          | S7             | S1                            | I(special form) |

## - 052 SO Si<exp Shift Si left jk places to SO

This instruction shifts Si left jk places and enters the result into SO. The assembler evaluates the expression to determine the shift count. All symbols in the expression must be previously defined. The shift count must be a positive integer not exceeding 64. If the shift count is 64, an 053 instruction is generated. The shift is end-off with zero fill. Si is not altered.

| Code Generated | location | result | operand                            | comments |

|----------------|----------|--------|------------------------------------|----------|

|                | 1        | 10     | 20                                 | 135      |

| 052305         |          | SO     | S3<5                               |          |

| 052012         |          | S0     | SO <d'10< td=""><td>1</td></d'10<> | 1        |

| 052760         |          | SO     | S7 <val< td=""><td>Ì</td></val<>   | Ì        |

| 053200         |          | SO     | S2<100                             |          |

#### - 053 SO Si>exp Shift Si right 64-jk places to SO

This instruction shifts Si right (64-jk) places and enters the result into SO. The assembler evaluates the expression to determine the shift count. All symbols in the expression must have been previously defined. The shift count must be a positive integer not exceeding 64. The assembler stores 64 minus the shift count in the jk field of the instruction. If the shift count is zero, an 052 instruction is generated. The shift is end-off with zero fill. Si is not altered.

Examples:

| Code Generated | location | result | operand | comments |

|----------------|----------|--------|---------|----------|

|                | 1        | 10     | 20      | 35       |

| 053373         |          | S0     | \$3>5   |          |

| 053066         |          | SO     | SO>D'10 |          |

| 053760         |          | SO     | S7>VAL  | l l      |

| 052100         |          | SO     | S1>0    |          |

- 054 Si Si<exp Shift Si left jk places to Si

This instruction shifts Si left jk places and enters the result into Si. The assembler evaluates the expression to determine the shift count. All symbols in the expression must have been previously defined. The shift count must be a positive integer not exceeding 64. If the shift count is 64, an 055 instruction is generated. The shift is end-off with zero fill.

Examples:

| Code Generated | location | result | operand  | comments |

|----------------|----------|--------|----------|----------|

|                | 1        | 10     | 20.      | 35       |

| 054703         |          | S7     | S7<3     |          |

| 054656         |          | S6     | S6-VAL+2 |          |

| 055300         |          | S3     | S3<100   |          |

- 055 Si Si>exp Shift Si right 64-jk places to Si

This instruction shifts Si right (64-jk) places and enters the result into Si. The assembler evaluates the expression to determine the shift count. All symbols in the expression must have been previously defined. The shift count must be a positive integer not exceeding 64. The assembler stores 64 minus the shift count in the jk field of the instruction. If the shift count is zero, an 054 instruction is generated. The shift is end-off with zero fill.

| 1 10<br>055775 S7<br>055656 S6 | 20       | 35       |

|--------------------------------|----------|----------|

|                                | 6752     |          |

| 055656                         | S7>3     | <b>1</b> |

|                                | S6>VAL+2 |          |

| 054300   34  S3                | S3>0     |          |

# - 056 Si Si,Sj<Ak Shift Si Sj left (Ak) places to Si

This instruction left shifts the 128-bit quantity formed by concatenating Si and Sj by the amount specified in Ak. The shift is end-off with zero fill. The high order 64 bits of the result are transmitted to Si. Si is cleared if the shift count exceeds 127. The shift is a left circular shift of Si if the shift count does not exceed 64 and the i and j designators are equal and non-zero. The instruction produces the same result as the 054 instruction if the shift count does not exceed 127 and the j designator is zero. The 128-bit quantity is shifted left one place if the k designator is zero.

#### Examples:

| Code Generated                       | location | result               | operand                                                                                                 | comments       |

|--------------------------------------|----------|----------------------|---------------------------------------------------------------------------------------------------------|----------------|

|                                      | 1        | 10                   | 20                                                                                                      | 35             |

| 056235<br>056604<br>056604<br>056774 |          | S2<br>S6<br>S6<br>S7 | S2,S3 <a5<br>S6,S0<a4<br>S6<a4<br>S7,S7<a4< td=""><td>(special form)</td></a4<></a4<br></a4<br></a5<br> | (special form) |

# - 057 Si Sj,Si>Ak Shift Sj Si right (Ak) places to Si

This instruction right shifts the 128-bit quantity formed by concatenating Sj and Si by the amount specified in Ak. The shift is end-off with zero fill. The low order 64 bits of the result are transmitted to Si. Si is cleared if the shift count exceeds 127. The shift is a right circular shift of Si if the shift count does not exceed 64 and the i and j designators are equal and non-zero. The instruction produces the same result as the 055 instruction if the shift count does not exceed 127 and the j designator is zero. The 128-bit quantity is shifted right one place if the k designator is zero.

| Code Generated                       | location re          | sult operand      | comments       |

|--------------------------------------|----------------------|-------------------|----------------|

|                                      | 1 10                 | 20                | 35             |

| 057235<br>057604<br>057604<br>057774 | S2<br>S6<br>S6<br>S7 | S0,S6>A4<br>S6>A4 | (special form) |

#### - 060 Si Sj+Sk Integer sum of Sj and Sk to Si

This instruction forms the integer sum of Sj and Sk and enters the result into Si. No overflow is detected. Sk is transmitted to Si if the j designator is zero and the k designator is non-zero. The high order bit of Si is set and all other bits of Si are cleared if the j and k designators are both zero. The j and k designators will normally be non-zero.

## Examples:

| Code Generated   | location | result   | operand        | comments |

|------------------|----------|----------|----------------|----------|

|                  | 1        | 10       | 20             | 35       |

| 060237<br>060405 |          | S2<br>S4 | S3+S7<br>S0+S5 |          |

#### - 061 Si Sj-Sk Integer difference of Sj and Sk to Si